コンピュータアーキテクチャの論文を読んでいたのだが、どうもよく知らない項目がある。 よく考えてみたらコンピュータアーキテクチャの最新トレンドも含め最近勉強量が不足していたので、ここらへんでもう一度復習しておきたい。 せっかくなので海外の大学の講義資料を読んでみよう。

- Advanced Computer Architecture

https://www.ece.ucsb.edu/~strukov/ece154BSpring2018/home.htm

せっかくなのでまとめていく。

目次

- 1. 半導体のトレンドと背景

- 2.半導体の性能向上

- 3.半導体の性能向上

- 4. キャッシュ階層

- 5. キャッシュ階層

- 6. 高度なキャッシュ最適化

- 7. ILPの向上テクニック

- 8. ILPの向上テクニック, Tomasuloのアルゴリズム

- 9. 分岐予測

- 10. 複数命令発行の技術

コンピュータのトレンド:(単一)プロセッサの性能

- 問題8:なぜダイサイズは年率10%で増加するのか?

- 単一のプロセッサの性能向上には、より多くのハードウェアが必要となる

- 大きなキャッシュ・より洗練された分岐予測器など。。。

- 単一のプロセッサの性能向上には、より多くのハードウェアが必要となる

集積路のコスト

Final Test yield : 最終的なテストを通過する確率

Die yield : ウェハ上のダイの非不良率 : [tex:\text{Wafer yield} \times 1 / (1 + \text{Defects per unit area} \times \text{Die area})N]

- Defects per unit area : 0.016 ~ 0.057 defects per square cm (2010)

はプロセスの複雑性の要因子: 11.5 ~ 15.5 (40nm, 2010)

ASIC vs. Microprocessor

- 一般的にASICとマイクロプロセッサでは同じタスクを実行するのにどちらが実行密度が高いか?

- ASIC

- 一般的にASICとマイクロプロセッサではエネルギー効率が高く性能が高いのはどちらか?

- ASIC

- ASICとマイクロプロセッサではどちらが製造コストが低いか?

- 製造量による。上記のグラフを参照のこと。

代表的なコンピュータのプラットフォーム

- ASIC : より高い性能密度、より高速

- FPGA : マイクロプロセッサとASICの中間

- マイクロプロセッサ:より高いフレキシビリティ

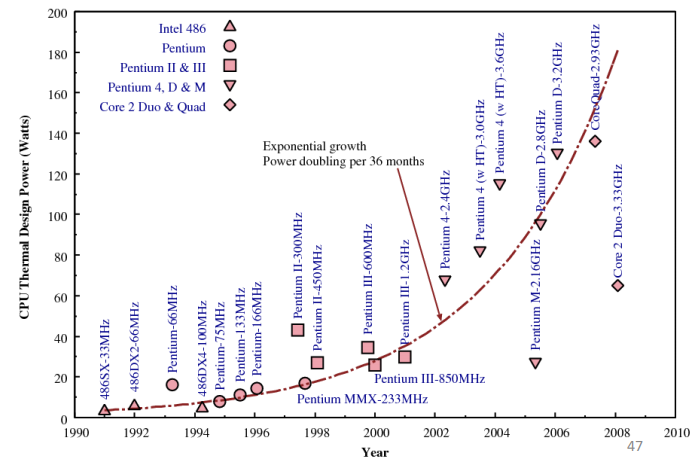

マイクロプロセッサの性能向上グラフについてもう一度

- 問題10:2002年以降にグラフはどのようになっているか?

Googleデータセンタにおける水冷システム

スタティック電力・ダイナミック電力

- スタティック電力は定常的に消費される電力。

ダイナミック電力はスイッチング時に消費される電力。

スタティック電力はVが小さくなると指数関数的に増大し、これを打ち消すことはできなくなる!→デナードスケーリングの終焉

スケーリングによる他の問題:トランジスタと配線

トランジスタと配線のサイズは、xy次元で決定される。1971年時は10マイクロメートルであったものが、2011年には0.032マイクロメートルまで縮小した。この時トランジスタは線形に性能を向上させたが、配線はそうもいかなかった。集積密度についてはトランジスタの縮小化により急激に増大したが、配線の遅延が改善しなかった。常に長配線が必要となってしまう。したがって、過去に比べて半導体をスケーリングさせることによる性能向上のメリットは小さくなりつつある。

50~80%のゲートがリピータであり、その数は増大している。プロセスを進めるために、より多くの空間と安全マージンが必要となっている。

消費電力を削減するための手法

なるべく何もしないように努める。つまり、DRAMやディスクにおいては待機状態を上手く確保して消費電力を避け、サーバなどのシステムに関しては特にタスクがない場合にはなるべく動かないようにする。また、スタティックな消費電力を削減するためにパワーゲーティングを適用するなどの最適化を行う。

電圧と消費電力の動的な最適化を行う。

オーバクロックし、他のコアをシャットダウンする。ターボブーストなど。

- 問題11:消費電力の観点からマルチプロセッサの利点は?

解答11:タスクが簡単に並列化可能ならば、

個のプロセッサを使えばより低い電圧(

)で、より低速な動作周波数(

)で動作させることができる。また、消費電力も同様に抑えることができる。

問題10:2002年以降にグラフはどのようになっているか?(再掲)

パイプライン化の終焉

- スーパスカラの限界

マイクロプロセッサにおけるトレンド

アーキテクチャにおける今後のトレンド

- 命令レベル並列性(ILP)をこれ以上向上させることはできない。

- 別の観点から性能を向上させる手法が中心となる。

マルチコアへの変遷

ダークシリコン問題

ある一定時間において、チップの一部分のみが活性化される。

つまり、マイクロプロセッサ内において専用回路が作られる。

新しいクラスのコンピュータ

ニューロコンピュータ・ニューラルネットワーク