コンピュータアーキテクチャの論文を読んでいたのだが、どうもよく知らない項目がある。 よく考えてみたらコンピュータアーキテクチャの最新トレンドも含め最近勉強量が不足していたので、ここらへんでもう一度復習しておきたい。 せっかくなので海外の大学の講義資料を読んでみよう。

- Advanced Computer Architecture

https://www.ece.ucsb.edu/~strukov/ece154BSpring2018/home.htm

目次

- 1. 半導体のトレンドと背景

- 2.半導体の性能向上

- 3.半導体の性能向上

- 4. キャッシュ階層

- 5. キャッシュ階層

- 6. 高度なキャッシュ最適化

- 7. ILPの向上テクニック

- 8. ILPの向上テクニック, Tomasuloのアルゴリズム

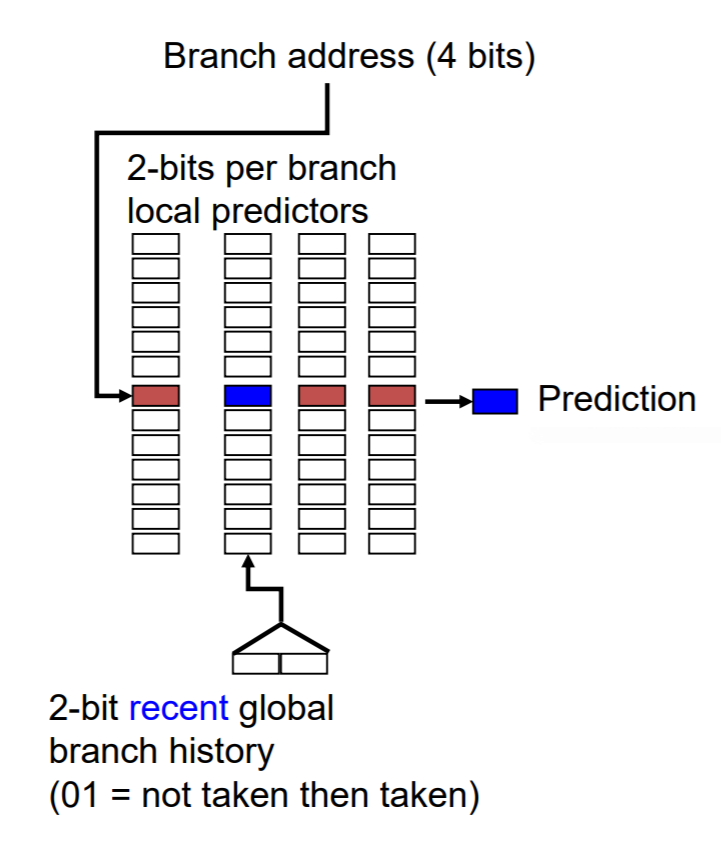

- 9. 分岐予測

- 10. 複数命令発行の技術

Advanced Computer Architecture

6. 複数命令発行

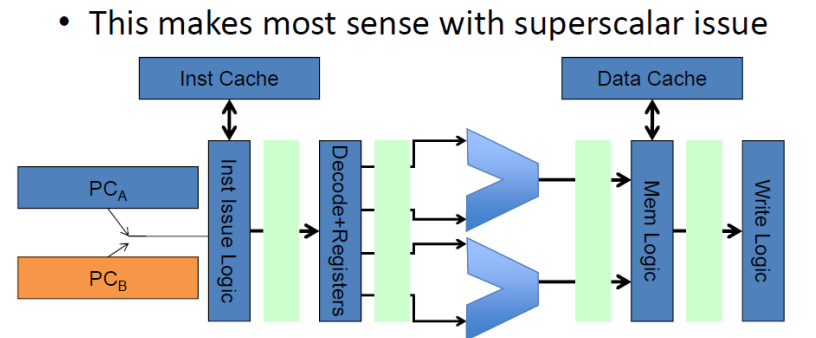

CPI<1を達成するためには、1命令あたりに複数の命令を発行する必要がある。このための解決方法として

- 静的にスケジューリングされるスーパスカラプロセッサ

- VLIW(Very long instruction worrd)プロセッサ

- 動的にスケジューリングされるスーパスカラプロセッサ

がある。順に紹介する。まずは、複数命令を発行するための技法についてまとめる。

| 名前 | 命令発行方針 | ハザード検出 | スケジューリング | 特徴 | 例 |

|---|---|---|---|---|---|

| スーパスカラ(静的) | 動的 | ハードウェア | 静的 | インオーダ実行 | 組み込み業界で使用される。MIPS, ARM, Cortex-A8 |

| スーパスカラ(動的) | 動的 | ハードウェア | 動的 | いくつかはアウトオブオーダ実行。ただし投擲的実行はしない | 存在しない。 |

| スーパスカラ(投機的実行) | 動的 | ハードウェあ | 投機的実行を使用した動的 | 投機的アウトオブオーダ実行 | Intel Core i3, i5, i7, AMD Phenom, IBM Power 7 |

| VLIW/LIW | 静的 | 主にソフトウェア | 静的 | 全てのハザードはコンパイラにより検出され調整される。 | 信号処理プロセッサ。TI C6xなど。 |

| EPIC | 主に静的 | 主にソフトウェア | ほとんど静的 | 全てのハザードはコンパイラにより明示的に検出され調整される。 | Itanium |

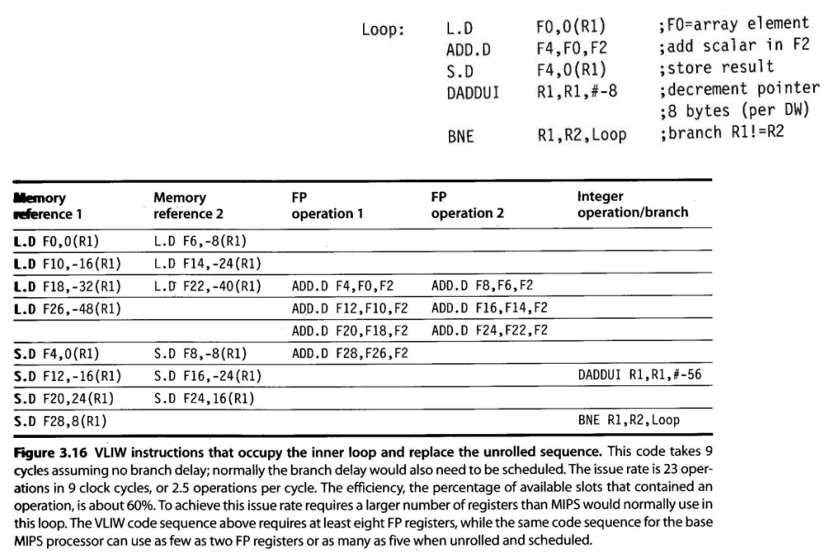

VLIWプロセッサ

複数の演算を1つの命令にまとめ上げる。

- 1つの整数命令(もしくは分岐命令)

- 2つの独立した浮動小数点演算

- 2つの独立したメモリ参照命令

コード内に十分な並列性を取得できる必要がある。VLIWの問題点としては、

- 静的に並列性を検出する必要がある。

- コードサイズが増加する傾向にある。

- ハードウェアによるハザード検出する機構が無い。

- バイナリコードの互換性がない。

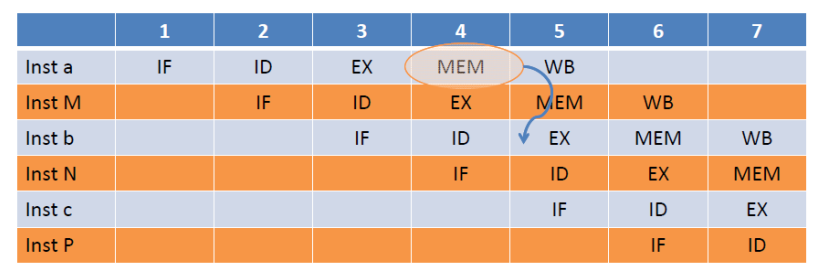

投機的実行を使用した動的スケジューリング、複数命令発行

現代のマイクロアーキテクチャが採用している手法。実現するためには、2つの方法がある。

- リザベーションステーションを割り当て、クロックの半分でパイプライン制御テーブルをアップデートする。

- 2命令/クロックしかサポートされない。

- 命令間の依存関係を処理するための論理を実装する。

- ハイブリッドな手法

命令発行ロジックがボトルネックとなりうる。

発行する命令の組を「バンドル」と呼ぶ。バンドル内のすべての命令の依存関係について検出する必要がある。もし依存関係がバンドル内に存在すれば、リザベーションステーション内でそれらを表現する。さらに複数かんりょう・複数コミットをサポートさせる。

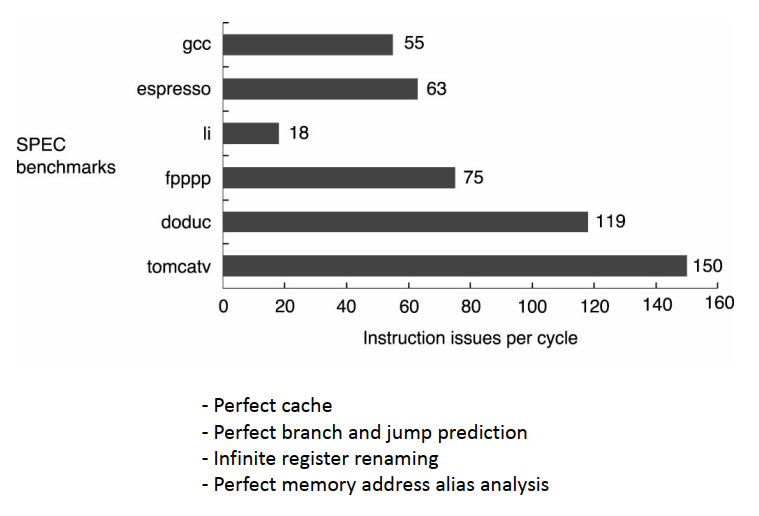

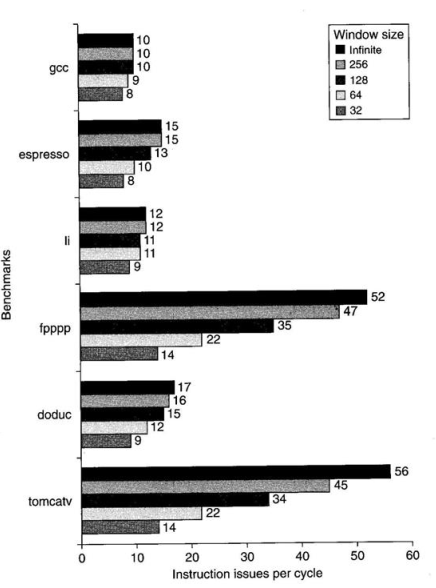

ILPの限界(理想状態)

実際のベンチマークではこのようになる。

マルチスレッドアーキテクチャのモチベーション

ハードウェアのもつ最大性能を達成することができない原因として、70年代まではメモリのレイテンシの影響が要因だった。しかし90年代になると、並列ハードウェアが複雑になっても、性能ハードウェアの複雑性に対して線形に増加しないという問題が発生した。

- 命令発行バンド幅が増加している。

- 機能ユニットの数が増加している。

- 命令がアウトオブオーダで実行され、インオーダで完了する。

これだけのハードウェアを投入すると、プロセッサのハードウェア使用率は減少し、命令発行幅に比例して命令のスループットが増加しなくなる。

したがって、一般的な解決方法としてよりスマートなキャッシュや、より精度の高い分岐予測器の実装が挙げられた。

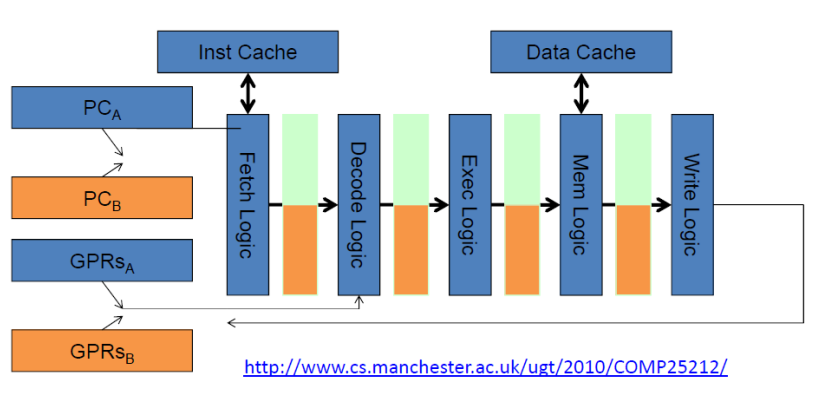

しかし、マルチスレッドプロセッサは全く異なるスレッドの独立した命令を同時に実行することで、プロセッサのストール要因を削減する。1つのスレッドだけでなく、複数スレッドのハードウェアを持つ。

- レジスタ

- プログラムカウンタ

- 各スレッド状態は「ハードウェアコンテキスト」と呼ばれる。

ソフトウェアのコンテキストスイッチングを行うことなく複数の命令ストリームを実行することで、ハードウェアの使用率を向上させる。

細粒度マルチスレッディングでは、CPUのスレッドを1サイクル毎に切り替えることでオーバヘッドを最小化する。これにより、各スレッド間のストールを隠蔽する。

粗粒度マルチスレッディングでは、CPUの1スレッドがストールすると、別のスレッドの命令を毎サイクル発行する。

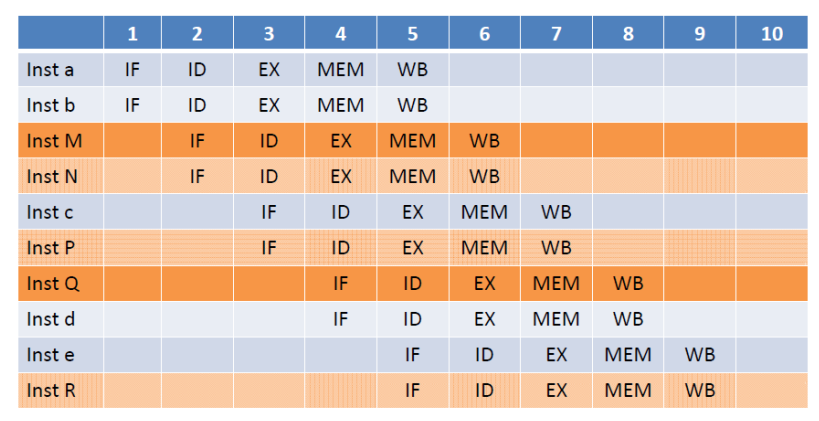

同時マルチスレッディングでは、同じパイプラインステージに複数のスレッドの命令が混在することを許可する。

- 粗粒度マルチスレッディング

- 細粒度マルチスレッディング

- 同時マルチスレッディング(SMT)

- 複数の命令を複数のスレッドから同じサイクルに発行する。

- ハードウェアのコンテキストスイッチングは行われない。

- 各スレッドの実行時間を増価させることなく、命令のスループットを向上させる。