RoCCへの接続方法について、少しずつ分かってきたので、独自Acceleratorを作って、接続してみたい。願わくば、FPGAで動作確認できるところまで行ってみたいな。

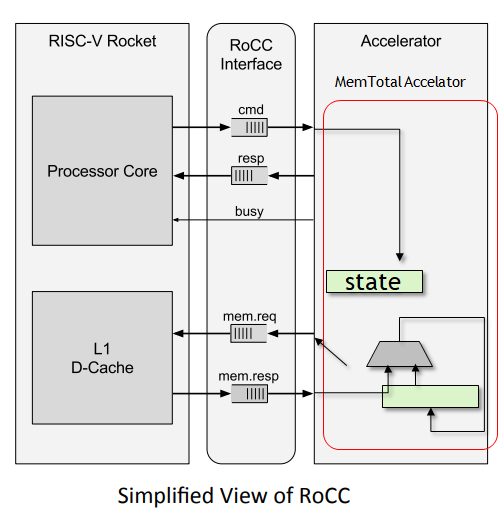

RoCC Interfaceについて

RoCCには、いくつかインタフェースが入っているが、大きく分けて使用するのは、

- io.cmd: Rocket Coreからの発行命令情報など。

- io.mem: L1キャッシュへのアクセスインタフェース

この2つが制御できれば問題ないと思われる。ここでは、オペランド値1で指定されたアドレスから、オペランド値2で指定されたサイズのデータをL1キャッシュから読み込み、値をすべて加算して返すという回路を作ってみたい。

最終的には、行列積を実行できる回路を作ってみたいが、これはまずは前哨戦。

MemTotal Acceleratorの概要

今回作ってみたいのは、L1キャッシュからデータを読み込んでそれを加算し、結果をRocket Coreに戻す命令。 用途的には全く意味が無いけれども、まずは簡単なものから。

ステートマシンの記述と、L1へのアクセスはサンプルデザインを元に作成した。

これを使ってテストを実行しているのだが、どうも上手く行かない。っていうか、コンパイルとシミュレーションは、しっかりとVerilogでシミュレーションするくらいに時間がかかる。 これならばVerilogを使った方がデバッグも楽だし分かりやすいんじゃ。。。とか思ったら負けなので、継続して試行していく予定。