RISC-VのオープンソースプロセッサBOOMv3(SonicBOOM)が公開されている。シミュレーションは前回上手く動作したが、ブロックダイアグラムを作って中身を見てみたいと思った。

そこで生成されたVerilogを読みながらブロックダイアグラムを作ってみることにした。すべて手書きである。 Chiselのコードを見ながら作るか、生成されたVerilogを読みながら作るかだが、Chiselはパラメータによって隠された部分が多量にあるのでおそらく細かな配線を見逃しやすい。 Verilogのコードは煩雑で非常に長いため解析に時間がかかるが、これまでも何度もChiselの生成したVerilogコードと格闘してきたため特に苦になる事は無い。Verilogを読んでいくことにした。

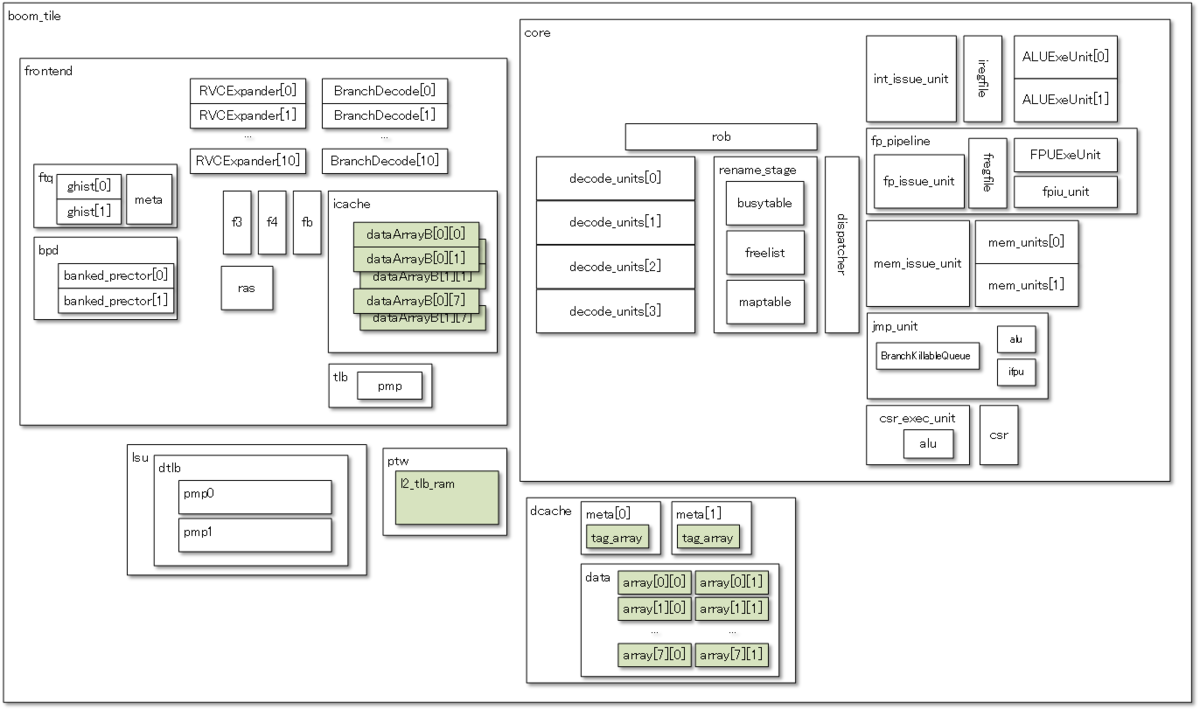

まずはコア内のブロックから。主にフロントエンド、バックエンド、LSU、キャッシュを分離して構成するのが伝統的なRocket-Chip系の実装方針になっている。緑で色付けしたのはSRAMに相当する部分。

次に各ブロック間のインタフェースについて。Verilogを読みながら配線幅の大きなところと、名前で何となく重要そうな信号を抜き出していってブロック間で配線を引いていった。

インタフェースはTileLink-Cの128ビットだ。それ以外の所は普通のValid/ReadyのIOで接続されている。LSUなどは64ビットのバスで構成され、命令はフロントエンドからバックエンドに4命令同時に渡されている。命令発行幅などの、コア内の詳細についてはまだ確認していない。