ChiselでSHA256の回路を設計するプロジェクト、Scalaでの検証用コードと、Chiselで書いたハードウェアを検証する。

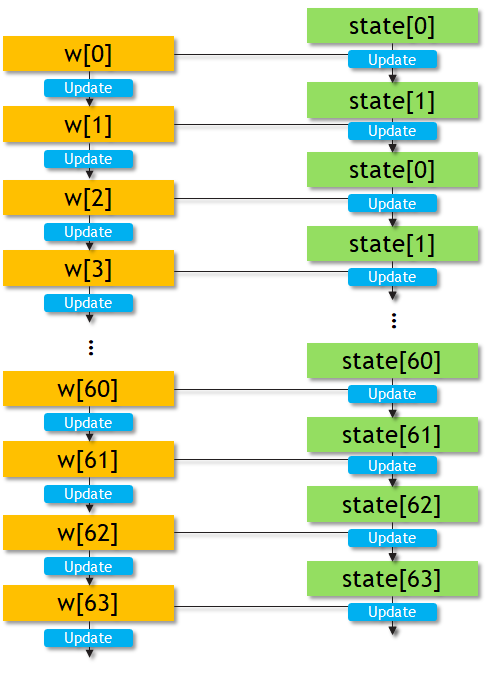

Chiselで書いたハードウェアは、SHA256のアルゴリズムで64回分ループを回す部分を展開し、パイプライン化した。 これにより、1サイクル毎にSHA256を計算できるマイニング用の回路として使用できる。

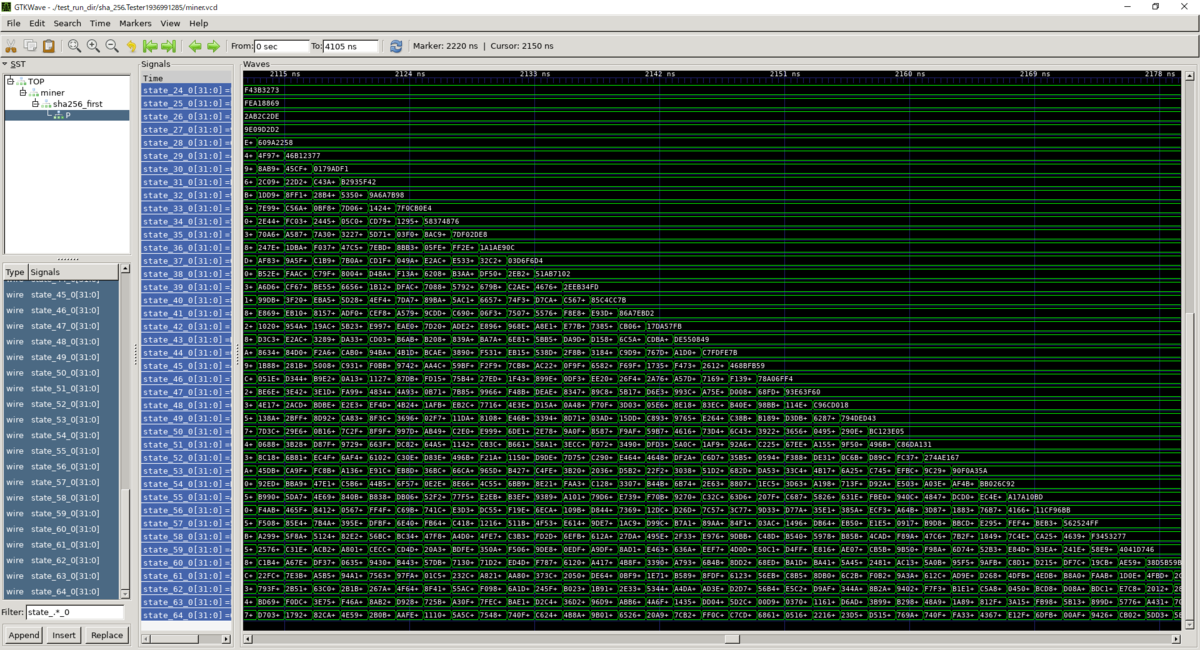

SHA256回路の検証は、Scala側のコードとChiselのコードを突き合せる形で行う。 しかし、Scalaのテストはシーケンシャルに記述する方法しか紹介されておらず、うまく検証コードを記述することができない。

SHA256回路の検証コードは未完成だが、とりあえず最初の32回分のSHA256の計算を突き合せて、一致することが確認できた。

ChiselコードとVerilogコードの検証速度比較

Chiselの速度を確かめるために、Verilatorを用いてChiselから生成されたVerilogコードのシミュレーションと、Chiselの状態でVerilogを使用せずに、Scalaの環境だけを使用した検証での速度を比較した。

- Scala環境 : Chiselのみ : Total time: 70[s]

- Verilator環境、波形なし : Total time: 427[s]

- Verilator環境、波形あり : Total time: 438[s]

Chiselのコードの方が速い。もっとも、ChiselからVerilogへの変換と、Verilatorのコンパイルに時間がかかっているように見えるが。。。