RISC-Vの実装、Rocket Chipのアクセラレータ向けインタフェースにハードウェアを実装し、RTLシミュレーションを行った。 次に、Rocket ChipをFPGA向けに論理合成するところまで上手く行ったので、今回開発したRoCCアクセラレータをFPGAに実装してみよう。 これで自作アクセラレータが正しく動作すれば、成功だ。

fpga-zynq で Rocket Chipリポジトリを差し替える

実際、Rocket Chipは結構な頻度で仕様や実装が変更されている。今回は割と最近のRocket Chipのリポジトリをベースにアクセラレータを開発した。 具体的には以下のコミットをベースに、ブランチを作って拡張を行っている。

しかし、fpga-zynqのリポジトリが現在サブリポジトリとして指定しているのはかなり古いrocket-chipのリポジトリだ。実際、半年前のRocket Chipの実装を指しており、このサブモジュールを最新までアップデートして論理合成を試行してみたのだが、上手く行かなかった。

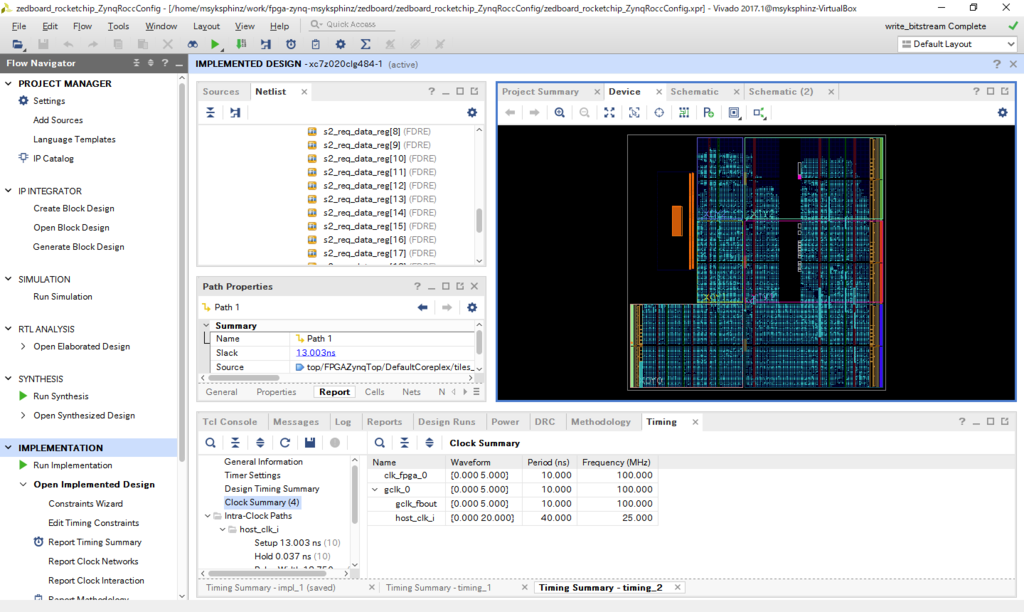

そこで、fpga-zynqが指しているRocket Chipのサブモジュールのリビジョンに、今回開発した自作アクセラレータの差分のみ適用し、そのまま論理合成を実行する。 この場合、RoCCアクセラレータのインタフェースとインスタンスの方法が少し変わっているため、そのままアクセラレータを乗せることはできなかったが、僅かな改変で一応、論理合成は上手く行ったようだ。

気になる動作周波数の方だが、そもそもRocket Chipの動作周波数が20MHzとなるようにクロック制約が組まれているため(!)、余裕でMetしている。 きちんと実装した行列演算アクセラレータも実装されているようだ。

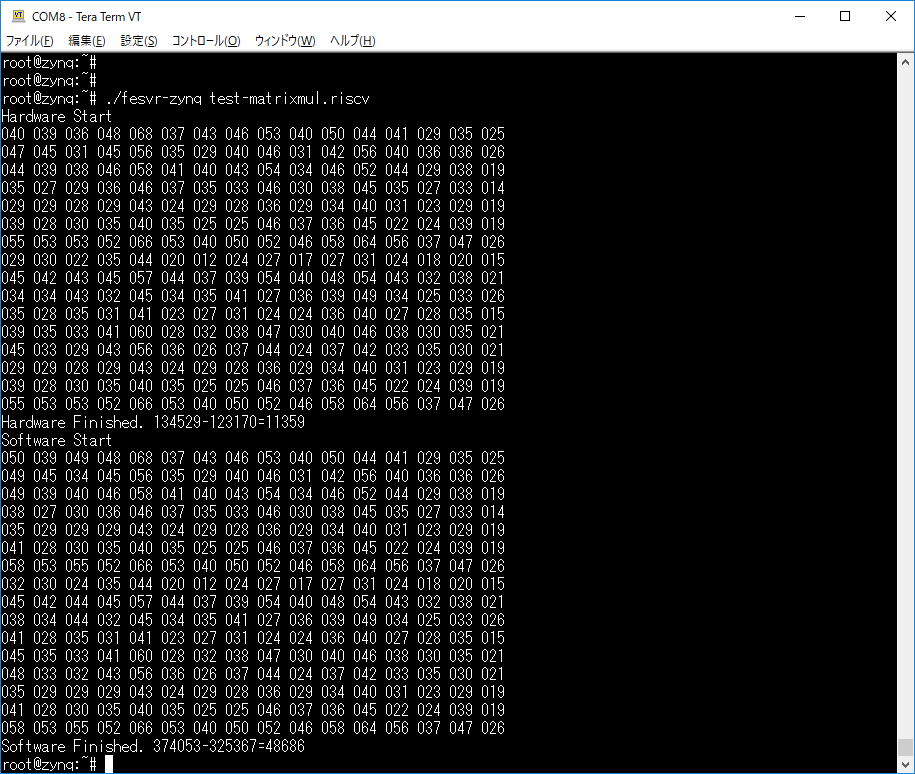

あとは、これをFPGAに実装して動作確認してみるだけとなる。いつものテストプログラムをSDカードに読み込んで、FPGAでLinuxをブートさせた。 そしてRocket Chipのフロントエンドサーバを起動させる。

root@zynq:~# ./fesvr-zynq test-matrixmul.riscv