この記事は ハードウェア開発、CPUアーキテクチャ Advent Calendar 2016 - Qiita の9日目の記事です。

Advent-Calendarを埋めてくれるかた、今からでも募集中です!是非参加してください! 僕一人では、クオリティのある記事を続けられそうにありません。。。(弱音)

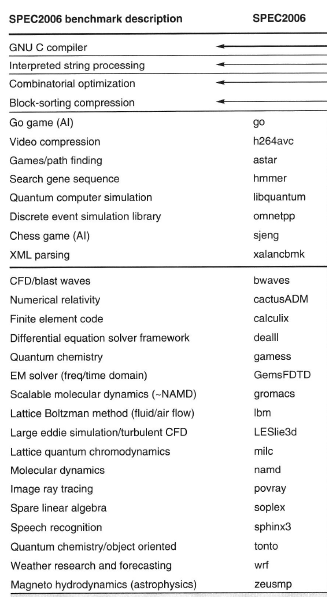

前回のベンチマーク紹介に続き、無料で使うことのできるベンチマークプログラムをコンパイルして、ZedBoardで動作させてみようと思う。

また、Verilogの本格的なシミュレータ環境を持っていなくても、Verilatorを使ってRISC-VのRocketチップを動作させることが出来る。

これについても、やり方を少し触れておきたい。

1. ZedBoard上のCortex-A9上でベンチマークを動作させる

ZedBoard上のZynqに搭載されているCortex-A9で、Linuxを動作させる記事は、既にかなりの量で紹介されている。

- ZedBoard用のUbuntu Linuxをビルド1(PLをビルド)

FPGAの部屋 ZedBoard用のUbuntu Linuxをビルド1(PLをビルド)

では、今回は立ち上がったLinux上でベンチマークを動作させようと思う。

Dhrystone ZedBoardで動作させる

Dhrystone自体は、SDカードにアーカイブを保存しておき、ZedBoard上のLinuxで展開する。

さらにコンパイルするためには、Makefileの-DTIMEのコメントアウトを解除する。-DTIMESのコメントアウトする。

バイナリが完成すると、実行してみる。最初にベンチマークの実行回数を入力する必要がある。ここでは、10000000 を指定した。

root@linaro-ubuntu-desktop:~/work# ./gcc_dry2

Dhrystone Benchmark, Version 2.1 (Language: C)

Program compiled without 'register' attribute

Please give the number of runs through the benchmark: 10000000

Execution starts, 10000000 runs through Dhrystone

Execution ends

Final values of the variables used in the benchmark:

Int_Glob: 5

should be: 5

Bool_Glob: 1

should be: 1

Ch_1_Glob: A

should be: A

Ch_2_Glob: B

should be: B

Arr_1_Glob[8]: 7

should be: 7

Arr_2_Glob[8][7]: 10000010

should be: Number_Of_Runs + 10

Ptr_Glob->

Ptr_Comp: 86024

should be: (implementation-dependent)

Discr: 0

should be: 0

Enum_Comp: 2

should be: 2

Int_Comp: 17

should be: 17

Str_Comp: DHRYSTONE PROGRAM, SOME STRING

should be: DHRYSTONE PROGRAM, SOME STRING

Next_Ptr_Glob->

Ptr_Comp: 86024

should be: (implementation-dependent), same as above

Discr: 0

should be: 0

Enum_Comp: 1

should be: 1

Int_Comp: 18

should be: 18

Str_Comp: DHRYSTONE PROGRAM, SOME STRING

should be: DHRYSTONE PROGRAM, SOME STRING

Int_1_Loc: 5

should be: 5

Int_2_Loc: 13

should be: 13

Int_3_Loc: 7

should be: 7

Enum_Loc: 1

should be: 1

Str_1_Loc: DHRYSTONE PROGRAM, 1'ST STRING

should be: DHRYSTONE PROGRAM, 1'ST STRING

Str_2_Loc: DHRYSTONE PROGRAM, 2'ND STRING

should be: DHRYSTONE PROGRAM, 2'ND STRING

Microseconds for one run through Dhrystone: 0.6

Dhrystones per Second: 1666666.6

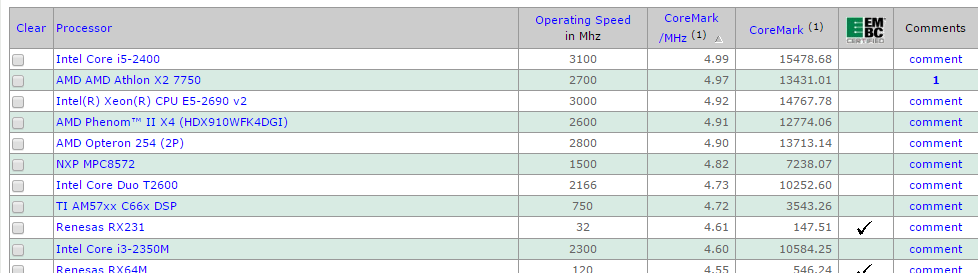

Coremarkを実行させる

Coremarkも同様に、Cortex-A9上のLinuxでコンパイルして実行できる。

make[1]: Leaving directory `/root/work/benchmarks/coremark_v./coremark.exe

2K performance run parameters for coremark.

CoreMark Size : 666ktop:~/work/benchmarks/coremark_v1.0# make PORT_DIR=linux c

Total ticks : 16252

Total time (secs): 16.252000

Iterations/Sec : 1845.926655

Iterations : 30000

Compiler version : GCC4.6.3

Compiler flags : -O3 -DPERFORMANCE_RUN=1 -lrt

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x5275

Correct operation validated. See readme.txt for run and reporting rules.

CoreMark 1.0 : 1845.926655 / GCC4.6.3 -O3 -DPERFORMANCE_RUN=1 -lrt / Heap

実際のところは性能はどうなのよ?

EEMBC - CoreMark - Processor Benchmark

Coremark Proを動作させる

こちらも同様に、Cortex-A9上のLinuxでコンパイルして実行できる。実行結果は以下のようになった。

UID Suite Name Contexts Workers Item Fails Time(secs) Iterations It/s Codesize Datasize Variance Standard Deviation #Results for run started at 70001:00:32:45 XCMD= 236760500 MLT cjpeg-rose7-preset 1 default 0 0.074 1 13.5135135135135 66495 266828 490760323 MLT core 1 default 0 9.37 1 0.106723585912487 42277 3688 1046644201 MLT linear_alg-mid-100x100-sp 1 default 0 0.135 1 7.40740740740741 45423 3388 1814569103 MLT loops-all-mid-10k-sp 1 default 0 3.04 1 0.328947368421053 54130 6912 549578576 MLT nnet_test 1 default 0 2.473 1 0.404367165386171 45041 42844 780641437 MLT parser-125k 1 default 0 0.351 1 2.84900284900285 52527 1468 1862946660 MLT radix2-big-64k 1 default 0 0.119 1 8.40336134453782 1420169 1712 1050863061 MLT sha-test 1 default 0 0.049 1 20.4081632653061 50823 1556 946108807 MLT zip-test 1 default 0 0.1 1 10 87499 1660

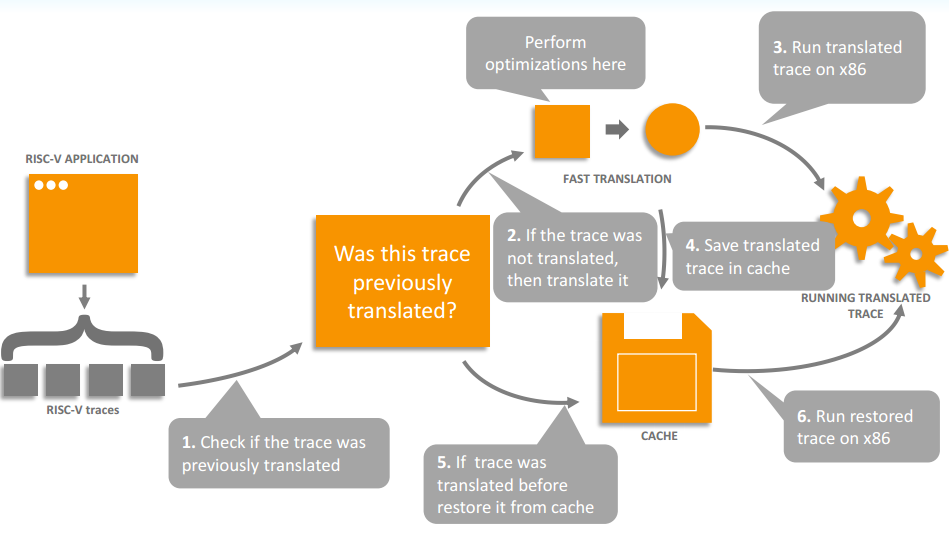

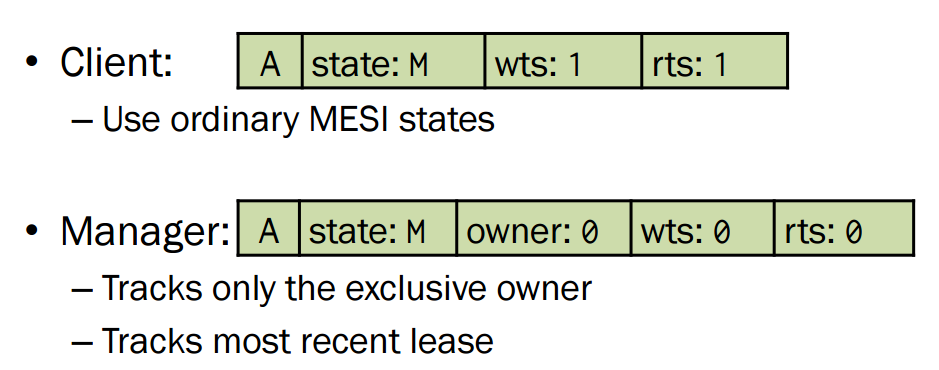

2. Rocket-ChipのRTLをVerilatorで動作させ、ベンチマークを実行したい。

本当は自分でコンパイルしたCoremarkをRTLで動作させたかったのだが、時間切れ。。。あとで追記したい。

RocketChipをRTLシミュレーションするための環境は既に構築されており、RocketChipのリポジトリをダウンロードするだけで良い。

VCSとVerilatorの方法が紹介されている。私はVCSなどという高価なシミュレータは持っていないので、無料のVerilatorを使って動作させたい。

Verilatorで(既にリポジトリに登録されている)ベンチマークを動作させる方法

cd $ROCKETCHIP/emulator make output/dhrystone.riscv

outputディレクトリには、dhrysoten.riscv(RISC-VでコンパイルされたDhrystone) バイナリが配置されており、このバイナリをロードして実行している。+verboseオプションが入っていると、output/dhrystone.riscv.outにパイプラインの動作結果が入っているはずだ。

using random seed 1481204383 C 0: 0 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 1 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 2 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 3 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 4 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 5 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 6 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 7 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 8 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 9 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 10 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 11 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 12 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4 C 0: 13 [0] pc=[01b275ab7a] W[r 0=0000000000000000][0] R[r30=47ed8219deb18ce6] R[r12=eec807c6a88f1dbd] inst=[d4cf0a6f] jal s4, pc - 0xfab4

訳わからないトレースログが出ているのだが、[1] pcでgrepすることで有効な命令を抽出することが出来る。

grep "\[1\] pc" dhrystone.riscv.out > dhrystone.riscv.inst

C 0: 120610 [1] pc=[00800011e4] W[r 0=0000000080002f40][0] R[r14=00000000800031e0] R[r15=0000000000000042] inst=[d6f70023] sb a5, -672(a4) C 0: 120611 [1] pc=[00800011e8] W[r 0=00000000800011ec][1] R[r 1=0000000080002130] R[r 0=0000000000000000] inst=[00008067] ret C 0: 120615 [1] pc=[0080002130] W[r15=4e4f545359524844][1] R[r 8=00000000800256b0] R[r 8=0000000000000003] inst=[f2843783] ld a5, -216(s0) C 0: 120616 [1] pc=[0080002134] W[r 9=0000000000000002][1] R[r 0=0000000000000000] R[r 2=0000000000000003] inst=[00200493] li s1, 2 C 0: 120617 [1] pc=[0080002138] W[r11=0000000080025620][1] R[r 8=00000000800256b0] R[r16=0000000000000003] inst=[f7040593] addi a1, s0, -144 C 0: 120618 [1] pc=[008000213c] W[r 0=0000000080025620][0] R[r 8=00000000800256b0] R[r15=4e4f545359524844] inst=[f6f43823] sd a5, -144(s0) C 0: 120650 [1] pc=[0080002140] W[r15=4152474f52502045][1] R[r 8=00000000800256b0] R[r 0=0000000000000000] inst=[f2043783] ld a5, -224(s0) C 0: 120651 [1] pc=[0080002144] W[r10=0000000080025600][1] R[r 8=00000000800256b0] R[r16=4e4f545359524847] inst=[f5040513] addi a0, s0, -176 C 0: 120652 [1] pc=[0080002148] W[r 0=00000000800255f4][0] R[r 8=00000000800256b0] R[r 9=0000000000000002] inst=[f4942223] sw s1, -188(s0) C 0: 120653 [1] pc=[008000214c] W[r 0=0000000080025628][0] R[r 8=00000000800256b0] R[r15=4152474f52502045] inst=[f6f43c23] sd a5, -136(s0) C 0: 120654 [1] pc=[0080002150] W[r15=20444e2732202c4d][1] R[r 8=00000000800256b0] R[r24=4152474f52502047] inst=[f3843783] ld a5, -200(s0) C 0: 120656 [1] pc=[0080002154] W[r 0=0000000080025630][0] R[r 8=00000000800256b0] R[r15=20444e2732202c4d] inst=[f8f43023] sd a5, -128(s0) C 0: 120657 [1] pc=[0080002158] W[r15=0000000049525453][1] R[r 8=00000000800256b0] R[r20=4152474f52502047] inst=[f3442783] lw a5, -204(s0) C 0: 120659 [1] pc=[008000215c] W[r 0=0000000080025638][0] R[r 8=00000000800256b0] R[r15=0000000049525453] inst=[f8f42423] sw a5, -120(s0) C 0: 120660 [1] pc=[0080002160] W[r15=000000000000474e][1] R[r 8=00000000800256b0] R[r18=4152474f52502047] inst=[f3245783] lhu a5, -206(s0) C 0: 120663 [1] pc=[0080002164] W[r 0=000000008002563c][0] R[r 8=00000000800256b0] R[r15=000000000000474e] inst=[f8f41623] sh a5, -116(s0) C 0: 120664 [1] pc=[0080002168] W[r15=0000000000000000][1] R[r 8=00000000800256b0] R[r17=000000000000474f] inst=[f3144783] lbu a5, -207(s0) C 0: 120667 [1] pc=[008000216c] W[r 0=000000008002563e][0] R[r 8=00000000800256b0] R[r15=0000000000000000] inst=[f8f40723] sb a5, -114(s0) C 0: 120668 [1] pc=[0080002170] W[r15=0000000000000001][1] R[r 0=0000000000000000] R[r 1=0000000000000003] inst=[00100793] li a5, 1 C 0: 120669 [1] pc=[0080002174] W[r 0=00000000800255fc][0] R[r 8=00000000800256b0] R[r15=0000000000000001] inst=[f4f42623] sw a5, -180(s0) C 0: 120670 [1] pc=[0080002178] W[r 1=000000008000217c][1] R[r31=00000000800256b3] R[r12=0000000000000003] inst=[92cff0ef] jal pc - 0xed4 C 0: 120732 [1] pc=[00800012a4] W[r 2=0000000080025510][1] R[r 2=0000000080025530] R[r 0=0000000000000000] inst=[fe010113] addi sp, sp, -32 C 0: 120733 [1] pc=[00800012a8] W[r 0=0000000080025520][0] R[r 2=0000000080025510] R[r 8=00000000800256b0] inst=[00813823] sd s0, 16(sp) C 0: 120734 [1] pc=[00800012ac] W[r 0=0000000080025518][0] R[r 2=0000000080025510] R[r 9=0000000000000002] inst=[00913423] sd s1, 8(sp) C 0: 120735 [1] pc=[00800012b0] W[r 0=0000000080025528][0] R[r 2=0000000080025510] R[r 1=000000008000217c] inst=[00113c23] sd ra, 24(sp) C 0: 120736 [1] pc=[00800012b4] W[r 8=0000000080025600][1] R[r10=0000000080025600] R[r 0=0000000000000000] inst=[00050413] mv s0, a0 C 0: 120737 [1] pc=[00800012b8] W[r 9=0000000080025620][1] R[r11=0000000080025620] R[r 0=0000000000000000] inst=[00058493] mv s1, a1 C 0: 120738 [1] pc=[00800012bc] W[r11=0000000000000059][1] R[r 9=0000000080025620] R[r 3=000000008000217f] inst=[0034c583] lbu a1, 3(s1) C 0: 120770 [1] pc=[00800012c0] W[r10=0000000000000052][1] R[r 8=0000000080025600] R[r 2=000000008000217f] inst=[00244503] lbu a0, 2(s0) C 0: 120771 [1] pc=[00800012c4] W[r 1=00000000800012c8][1] R[r31=0000000080025603] R[r29=000000008000217f] inst=[fbdff0ef] jal pc - 0x44

ちなみに、Dhrystoneは以下のディレクトリでコンパイルされており、これを真似るとCoremarkもコンパイル出来るはずなのだが。。。

cd rocket-chip/riscv-tools/riscv-tests/benchmarks/

make