この記事は ハードウェア開発、CPUアーキテクチャ Advent Calendar 2016 - Qiita の7日目の記事です。

Advent-Calendarを埋めてくれるかた、今からでも募集中です!是非参加してください! 僕一人では、クオリティのある記事を続けられそうにありません。。。(弱音)

A FastInstruction Set Simulator for RISC-V (Esperanto)

Esperantoというスタートアップ企業で開発されている高速RISC-V命令セットシミュレータの紹介。

RISC-Vの命令セットシミュレータといえば、riscv-spikeが存在する。これは UC-Berkeleyで開発された本家のISSだ。また、RISC-V向けのQEMUも存在する。

これらのシミュレータは、例えばSPECINTを実行させた場合に、シミュレーションだけだと非常に遅いという欠点がある。例えば、実CPUでx64で動作させると一瞬なのだが、ISSで動作させると非常に時間がかかったり、そもそもQEMUで実行するとFailになったりする。

これを解決するために、EsperantoのFast Instruction Set Simulatorでは以下の部分に着目した。

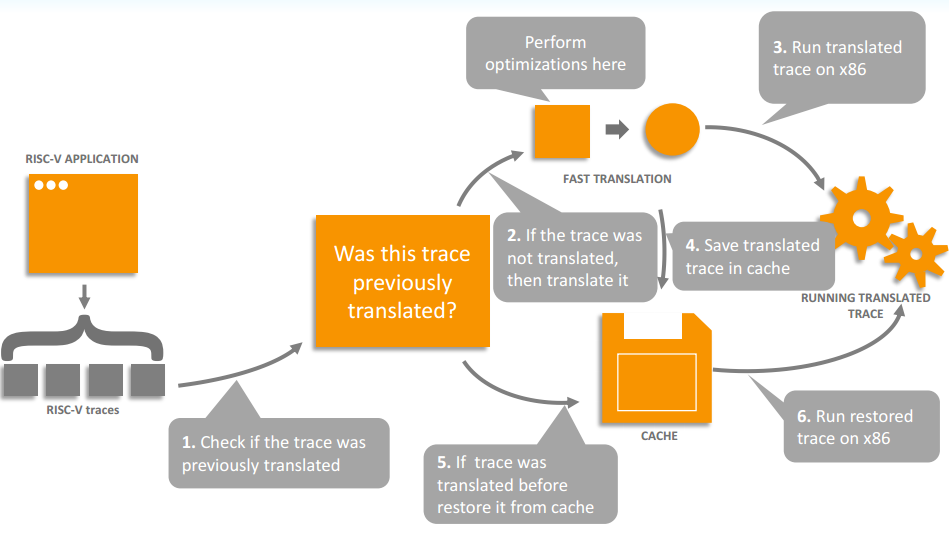

シミュレーション時の、RISC-V命令の変換フローは以下のようになっている。

これを見ると、もちろん命令の変換というのも実行されるのだが、一度変換した命令は、キャッシュに保存しておくことで冗長に変換処理を繰替えすことを防いでいる。

結果として、EsperantoのISSは、Nativeのx86でのベンチマーク実行と比較して、1/2.47倍の速度で実行できるようになった。 これは結構凄い結果だと思う。単純なISSでは決してここまで速くなることはないと思うのだが、Native命令に変換し、キャッシュを挿入することでNativeハードウェアと遜色無い性能にまで引き上げている。

ただし、手法自体はそこまで新しいものでは無いと思う。ターゲットの命令を、ホストPCの命令に変換し、これをキャッシュに格納して高速化することは、エミュレーションの本の最初の方にも説明があった気がする。 確か、以下の本だ。

- Virtual Machines: Versatile Platforms for Systems and Processes

- 作者: Jim Smith,Ravi Nair

- 出版社/メーカー: Morgan Kaufmann

- 発売日: 2005/07/12

- メディア: Kindle版

- この商品を含むブログを見る