RVCの判定条件に付いて,もうちょっと考え直した.

ある16ビット命令グループが,命令の下位16ビットグループであるというのは,以下の条件のどちらかであるはずだ.

これを, inst_16bit_valid[7:0] として,inst_16bit_valid[i] が命令の下位16ビットグループである条件は,

- すぐ前の16ビットグループが,RVIの上位16ビットである.つまり,

inst_16bit_valid[i-1] == 0 - すぐ前の16ビットグループが,RVCである.つまり

inst_rvc[i-1] == 1

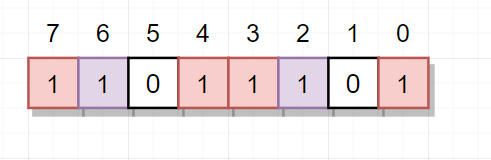

前回と同じ状況化を考えよう:inst_rvc[7:0]の結果が以下で,紫色のビットが,誤って判定されてしまった部分.上記の計算式をそのまま当てはめて修正する.

logic [ 7: 0] insn_rvc = 8'b1101_1101;

inst_16bit_valid[0] = 1'b1; // ビットのMisalignが起きていないと仮定 => RVC inst_16bit_valid[1] = ~inst_16bit_valid[0] | insn_rvc[0] = 1'b0 | 1'b1 = 1'b1; // RVIの先頭 inst_16bit_valid[2] = ~inst_16bit_valid[1] | insn_rvc[1] = 1'b0 | 1'b0 = 1'b0; inst_16bit_valid[3] = ~inst_16bit_valid[2] | insn_rvc[2] = 1'b1 | 1'b1 = 1'b1; // RVC inst_16bit_valid[4] = ~inst_16bit_valid[3] | insn_rvc[3] = 1'b0 | 1'b1 = 1'b1; // RVC inst_16bit_valid[5] = ~inst_16bit_valid[4] | insn_rvc[4] = 1'b0 | 1'b1 = 1'b1; // RVIの先頭 inst_16bit_valid[6] = ~inst_16bit_valid[5] | insn_rvc[5] = 1'b0 | 1'b0 = 1'b0; inst_16bit_valid[7] = ~inst_16bit_valid[6] | insn_rvc[6] = 1'b1 | 1'b1 = 1'b1; // RVC fragmented = ~(~inst_16bit_valid[7] | insn_rvc[7]) = inst_16bit_valid[7] & ~insn_rvc[7] = 1'b1 & 1'b0 = 1'b0;

とできるのではないか.論理としては下位ビットから上位ビットまでつながってしまうのだけれども,最小限に抑えることができるかな.