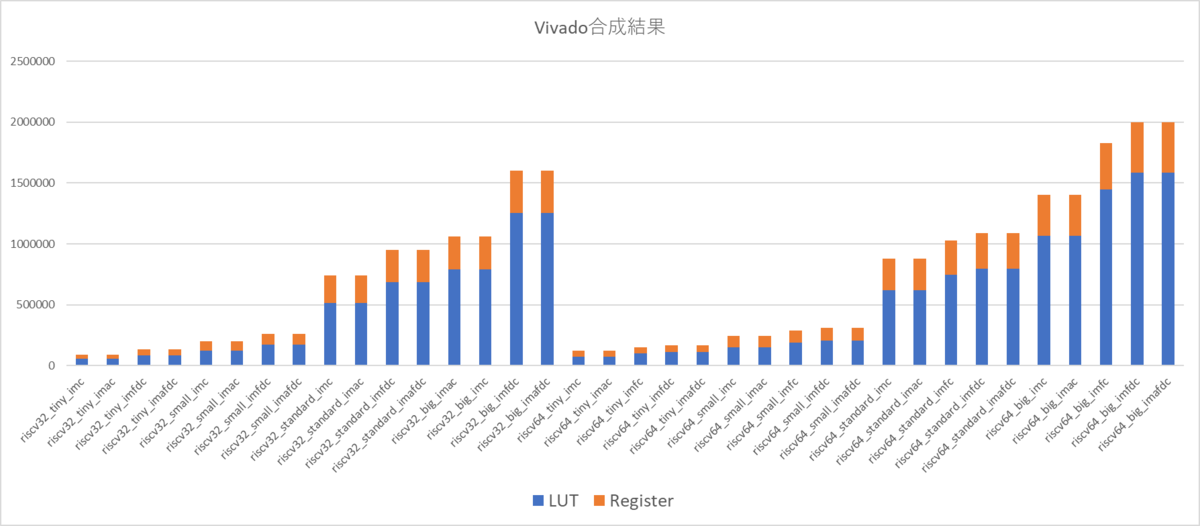

自作CPUで、いくつかのコンフィグレーションでVivadoの論理合成を試してみている。

コンフィグレーションの数自体は50種類くらいあるのだが、とりあえず論理合成の終わったものだけでグラフを作ってみた。

ちなみに、タイミングの設定方法は、なぜか制約が効いていないので今は何も考えていない。クロックは定義しているが、全体的にピンを設定していないのと、明らかに小さめのFPGAを使っているのでとりあえずタイミングのことは無視している。

とりあえずコンフィグレーションで面積がスケールすることを確認したかったので、適当にグラフを作った。

とりあえず気が付いたことは、

- Compressed命令が取り外せるかどうかでコンフィグレーションを分けたほうがいいかも

- Atomicの分別はコンフィグレーションを作るのを忘れた

- RV32のIMFCコンフィグレーションでは、論理合成できないバグがあった

- RV64で、IMFDCとIMFCコンフィグレーションでは一応面積がスケールした

などなど。とりあえずバグを直すところからだな。あとはSoC環境を早く用意しないと、まともにFPGAに乗せる環境にならない。 Chipyardが使えればいいけど、Chiselが嫌なのでもっとまともな汎用SoC環境はないかな。