なんとなく最近のコンピュータアーキテクチャ系の研究傾向が知りたいので、学会のサーベイをしてみることにした。

ICCADの併設されているWOSET、オープンソースのEDAツール系のワークショップで、面白そうな話がたくさんある。

WOSETのAbstractを読みながら何となく概要をつかんでいく。と言っても、大半はDeepLのお世話になっている。

「作ってみた」系が多いかな。

- WOSET: Workshop on open source EDA technologies (co-located)

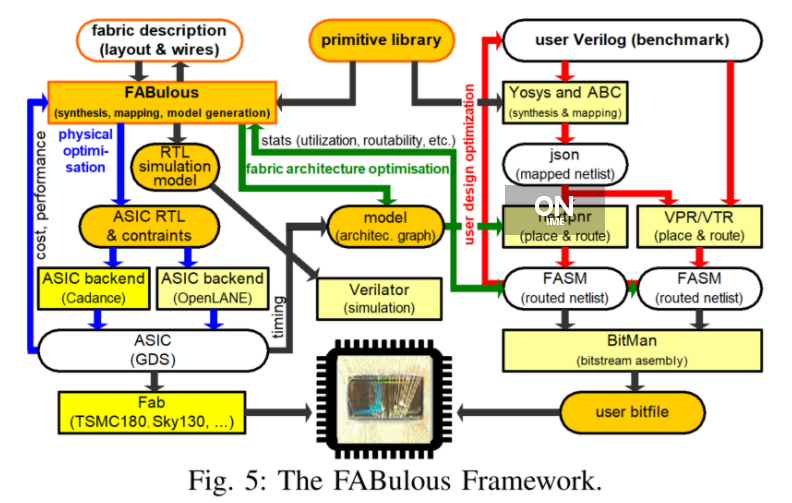

- FABulous: An Open-Everything Framework For Embedded FPGAs

- The University of Manchester, UK

- 本論文では、論理集積度、性能、消費電力などの面で、使いやすさと優れた品質を目指して設計された、オープンソースの組み込みFPGAフレームワークFABulousを紹介します。FABulousは、ロジック、メモリ、演算、各種IOの事前定義されたタイルからファブリックを構築することができます。タイルは必要に応じてレゴのようにつなぎ合わされます。ユーザーは、カスタムタイルを追加したり、配線リソースやFPGAファブリックのほとんどのアーキテクチャの詳細をカスタマイズすることができます。経験豊富な設計者は、コンフィギュレーションの保存やスイッチングに最適化されたセルを提供できます(例えば、パストランジスタ・マルチプレクサなど、当社が現在TSMC 180nmとSkywater 130nm向けに提供しているもの)。また、FABulousはスタンダードセル設計に戻ることも可能であり、これによりFABulous FPGAは異なるテクノロジーノード間で容易に移植することができます。FABulousは、低消費電力のフレームワイズリコンフィギュレーションやダイナミックパーシャルコンフィギュレーションなど、他のオープンソースFPGAフレームワークにはないユニークな機能を備えています。FABulousは、他のいくつかのオープンソースプロジェクト(Yosys、nextpnr、VPR、OpenLane、Verilator)を統合して、完全でオープンなエンドツーエンドのユーザーエクスペリエンスを提供します。

- 組み込みFPGAフレームワーク。FPGAを作ることができるということ?

- TSMC 180nmとSkywater 130nmを使ってテストした。

- FPGAファブリックを最適化するためのフレームワーク

- FABulous: An Open-Everything Framework For Embedded FPGAs

- **タイルの定義**

- **ファブリックの定義**

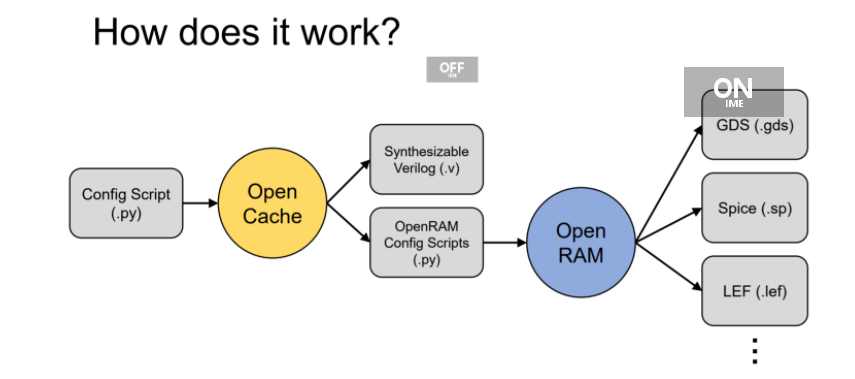

- OpenCache: An Open-Source OpenRAM Based Cache Generator

- Ozyegin University, UC Santa Cruz

- 大規模なメモリブロックの平均待ち時間を最大化するために、ハードウェアキャッシュが使用される。クライアントロジックは通常CPUコアであるが、アプリケーション固有のロジックである場合もある。しかし、キャッシュを一から手動で設計することは困難である。本論文では、オープンソースのパラメタライズドIPコア生成ツールであるOpenCacheを説明する。OpenCacheは、OpenRAMの効率問題を考慮しつつ、OpenRAMをオンザフライで呼び出す。OpenCacheの現在のバージョンは、クライアント側で単一のパイプラインとインオーダの読み書きポートをサポートしています。キャッシュロジック用の合成可能なVerilogモジュールと、生成されたキャッシュのデータとタグを保持する内部SRAMブロックをコンパイルするためのOpenRAM用設定ファイルを出力します。

- Towards Fast And Accurate Parallel Chip Thermal Simulations With PACT

- ここ数十年、チップ温度は、高性能でコスト効率に優れ、信頼性の高い集積回路(IC)を設計するための最も重要な基準の一つとなっています。消費電力と温度の増加は,チップの性能を低下させるだけでなく,より大きなサブスレッショルドリーク電力を発生させ,信頼性の問題を引き起こす。そのため、熱解析はチップを設計する上で必要不可欠な手順となっています。従来の熱解析は、有限要素法(FEM)ベースのマルチフィジックスシミュレーター(COMSOLやANSYSなど)に依存していました。このような市販のシミュレータは、計算コストが高く、解答時間が長く、必要なメモリ量も多いという問題があります。これらの制限により、市販のシミュレーターは多くの設計案や実行シナリオの評価には不向きです。したがって、高速かつ正確な熱解析は、チップ設計と熱最適化にとって非常に重要です。この論文では、SPICEベースのPArallel Compact Thermalシミュレータ(PACT)の主要機能について説明します。PACTは、スタンダードセルからアーキテクチャレベルまで、定常および過渡の並列熱シミュレーションを高速かつ正確に実現します。

- A Guide For Rapid Creation Of New HDLs

- 新しいHDLを素早く構築し、テストするためのガイドを紹介します。今後登場するHDLは、それぞれ専用に設計されたコンパイラが存在するため、重複した労力が必要となります。提案するガイドラインは、これらの努力を最小限に抑えることができます。新しい言語の開発者は、既存のコンパイラのインフラを利用して、新しいHDLとのインターフェイスを構築することができます。このインタフェースにより、開発者はリファレンスコンパイラなしでLECを使用することが可能になる。また、開発したHDLを、インターフェースされたコンパイラがサポートする他の言語へ変換することも可能である。また、このシステムにより、言語とインタフェースに対する高い信頼性を確保することができる。

- LEC : Logical Equivalent Check

- LECがやりやすくなる方法の調査?

- Y-flowからX-langを定義するためのフロー

- X-langからX-lang LECを生成する

- X-langからVerilogテスト

- ランダムプログラム生成

- 最終的にVerilogが生成されるのでこれを比較するところは変わらない?

- SystemVerilog IDE Integration With Verible Language Server Support

- Veribleは、SystemVerilogのためのオープンソースの開発者用生産性向上ツールです。自動修正パッチ、フォーマット、コード索引を含むリンティングと、プロジェクト検査ツールを提供します。

- githubアクションとの統合により、継続的インテグレーションでの自動実行やプルリクエストへのコメントが可能となり、開発チームにおけるコード品質の向上に貢献します。

- これまでは、いずれも静止しているファイルに対するオフラインでの利用でしたが、コードを書きながらのツールサポートは、Veribleが開発者の生産性を向上させるもう一つの方法です。IDE上で直接「定義にジャンプ」などのオンラインシンボルナビゲーションやコード品質のフィードバックを提供することは、Veribleが新たに開発した機能です。言語サーバプロトコルを使用することで、この機能は一般的なIDEと互換性を持っています。

- 本発表(Work-in-progressカテゴリに投稿)では、言語サーバプロトコルとIDEの統合の現状を含め、Veribleツールセットの様々な機能の使用方法をハンズオンで紹介します。

-

- RTLFuzzLab

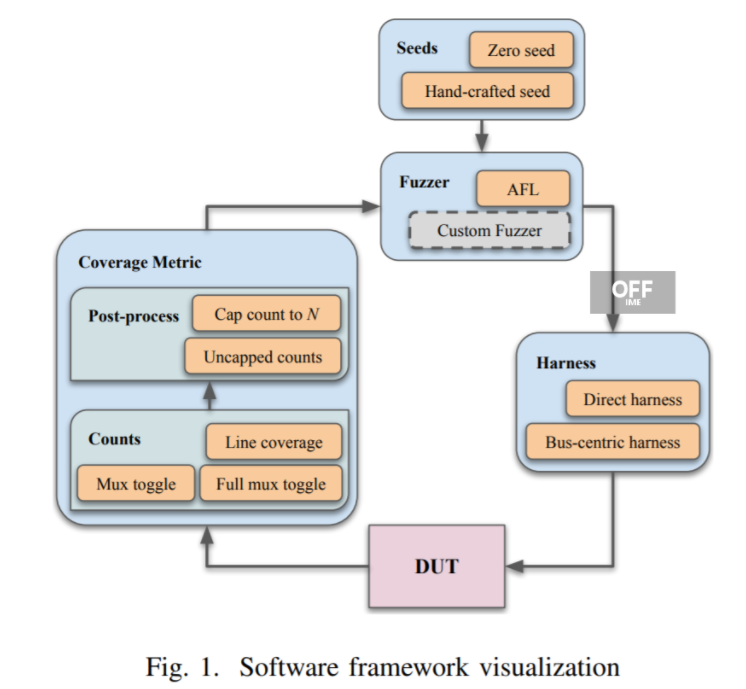

- カバレッジ指向変異ファズテストは、ソフトウェアの自動テストとバグ検出のための一般的なツールとなっています。この技術は、プログラムへの入力を提供し、それらのシード入力の実行中にテスト対象プログラムのどのブランチが探索されるかを測定することで機能する。次にファザーは、一連の決定論的および非決定論的な変異操作を適用することによって、元の入力を自動的に変異させます。テスト対象のプログラムは、これらの新しく生成された変異入力で実行されます。新しい入力は、今まで見られなかった分岐をカバーする場合、あるいはある分岐がカバーされる回数が大幅に増加する場合に限り、新しい変異の開始点として保持されます。変異した入力の大部分は、カバレッジを向上させないため、直ちに破棄されます。この自動ファジングは、無数のソフトウェアのバグを発見するのに非常に成功していますが、デジタルハードウェア設計のテストにはまだ浸透していません。

- ソフトウェアテストに使用されるファジングアルゴリズムをレジスタトランスファーレベル(RTL)設計に適用した最初の研究では、ハードウェアコンテキストで直面するさまざまな自由度が追加されていることが説明されました[1]。重要な決定の1つは、ソフトウェア・ファザーによって提供されたバイト列をどのように取り込み、テストベンチで使用するかということです。最も単純な解決策は、テスト対象の設計の入力配線に新しいデータを適用し、ファザーから提供されるデータを使い切ったらテストの実行を停止することです。より最近の研究では、文法を使用して、生のバイトを読み取りまたは書き込みのタイルリンクトランザクションに変換することが提案されています[2]。もう一つの問題は、ファザーへのフィードバックとしてどのようなカバレッジメトリックを使用するかということです。最初の論文では、マルチプレクサ制御信号のトグル数をカウントしましたが[1]、その後の論文では、完全なトグルのみをカウントすること[3]、またはRTL記述のラインカバレッジの代理としてソフトウェアシミュレーションモデルのブランチカバレッジを使用すること[2]が提案されています。また、ファジングを開始する初期入力シードの選択も結果に影響を与える可能性があります。

- RTLFUZZLABは、FIRRTL RTLコンパイラのインフラストラクチャ[4]に基づくオープンソースのフレームワークで、新しいファジングのアイデアを容易に探求することができます。私たちは、一般的なAFLファザーを簡単に統合し、独自のファザー実装を追加して、カスタム変異やファズスケジューラー設計を実験できるように取り組んでいます。私たちのダイレクトハーネスはRfuzz論文[1]のアイデアに基づいており、単一の入力クロックとリセットを持つ任意のRTL回路で動作します。このハーネスは、Fuzzing hardware like software [2]のタイルリンク専用ハーネスを再実装したバスセントリックハーネスに簡単に変更することが可能です。mux toggle coverage [1]、full mux toggle coverage [3]、HDL line coverage (2]で使用されたカバレッジに近似) など、様々なカバレッジ・メトリクスを提供します。これらのカバレッジメトリクスは後処理関数と組み合わせることができ、任意の組み合わせをファザーへのフィードバックとして選択することが可能です。また、いくつかの簡単なベンチマークと、ベンチマークを実行し結果を解析するスクリプトも含まれており、新しいファジングのアイデアを簡単にプロトタイプ化することができます。コードはBSDライセンスのもとでオープンソース化されており、GitHubで公開されています: [https://github.com/ekiwi/rtl-fuzz-lab](https://github.com/ekiwi/rtl-fuzz-lab)