Amazon AWS F1インスタンス上で動作するRocket-Chip環境、FireSimはRTLシミュレーション環境が用意されている。

チュートリアルを試しながら、さっそく実行してみよう。

- Debugging & Testing with RTL Simulation Debugging & Testing with RTL Simulation — FireSim documentation

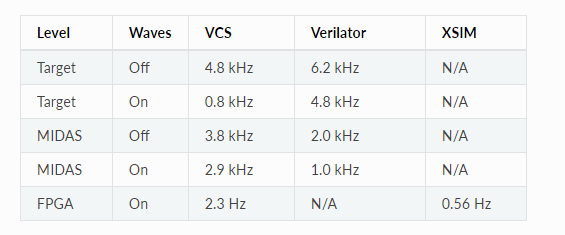

FireSimのRTLレベルシミュレーションの分類

FireSimには、いくつかのRTLレベルシミュレーションの分類があるらしい。

- ターゲットレベル(Target-Level) : RTLレベルで、Rocket-Chipのシミュレーションを行う。ホストレベルでのデバッグ機能は存在しない。

- サポートしているシミュレーションツール : VCS / Verilator

- MIDAS-Level : RTLレベルのシミュレーションで、MIDASにより変換される。FPGAをホスティングするシミュレーションモデルが再現されている。ターゲットのクロックとホストのクロックは同期している。DRAMやメモリマップドIO/PCIsなども使用することができる。

- サポートしているシミュレーションツール : VCS, Verilator

- FPGAレベル : 完全なFPGA環境でのシミュレーション。クロックドメイン通信やPLL, DRAMやPCI-EなどのFPGAペリフェラルを含んでいる。AWSにより提供されるシミュレーションレベル。

- サポートしているシミュレーションツール : VCS, Vivado XSIM

まずは、MIDAS-LevelでのRTLシミュレーションを実行してみる。

MIDAS-LevelでのRTLコンパイル

firesimのリポジトリをダウンロードしておく。さらに、RISC-Vのツールのコンパイル環境としてRISCVを設定しておく。

$ printenv RISCV /home/msyksphinz/riscv64/

シミュレーション環境に移行して、コンパイルを実行する。ここでは、Verilatorを使用した。 ちなみに、Verilatorのインストールはあらかじめ行っておく必要があるようだ(Rocket-Chipの環境では勝手にVerilatorまでダウンロードしていたんだけど...)

$ sudo apt install -y verilator $ cd firesim/sim $ make DESIGN=FireSimNoNIC

MIDAS-LevelでのRTLシミュレーション

RTLシミュレーションはRocket-Chipの環境と少しやり方が異なる。 例えば、Dhrystoneを実行したい場合、

- Rocket-Chip環境の場合

$ make output/dhrystone.riscv.out

- FireSim環境の場合

$ make DESIGN=FireSimNoNIC ${PWD}/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.out

FireSimの環境で実行すると、以下のように正しく動作してそうなのだが、最後にエラーとなった。

$ make DESIGN=FireSimNoNIC ${PWD}/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.run mkdir -p /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig ln -fs /home/msyksphinz/riscv64//riscv64-unknown-elf/share/riscv-tests/benchmarks/dhrystone.riscv /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv cd /home/msyksphinz/work/firesim/sim/generated-src/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/ && \ ./VFireSimNoNIC /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv +sample=/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.sample +max-cycles=100000000 +mm_relaxFunctionalModel=0 +mm_writeMaxReqs=16 +mm_readMaxReqs=16 +mm_writeLatency=30 +mm_readLatency=30 +dramsim \ 2> /dev/null 2> /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.run && [ $PIPESTATUS -eq 0 ] Microseconds for one run through Dhrystone: 469 Dhrystones per Second: 2128 mcycle = 234976 minstret = 196530 /bin/sh: 3: [: -eq: unexpected operator Makefile:171: recipe for target '/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.run' failed make: *** [/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.run] Error 2

一応、全体ベンチマークを流してみるのだが、どうもMakefileに問題がありそうだ?

$ make DESIGN=FireSimNoNIC run-bmark-tests cd /home/msyksphinz/work/firesim/sim/generated-src/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/ && \ ./VFireSimNoNIC /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/mm.riscv +sample=/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/mm.riscv.sample +max-cycles=100000000 +mm_relaxFunctionalModel=0 +mm_writeMaxReqs=16 +mm_readMaxReqs=16 +mm_writeLatency=30 +mm_readLatency=30 +dramsim \ 3>&1 1>&2 2>&3 | /home/msyksphinz/riscv64/bin/spike-dasm > /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/mm.riscv.out && [ $PIPESTATUS -eq 0 ] C0: reg block 4x5x6, cache block 24x25x24 C0: 24811 instructions C0: 26056 cycles C0: 28800 flops C0: 1105 Mflops @ 1 GHz /bin/sh: 3: [: -eq: unexpected operator Makefile:176: recipe for target '/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/mm.riscv.out' failed make: *** [/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/mm.riscv.out] Error 2

試しに、最後の$PIPESTATUSを表示してみた。

$ make DESIGN=FireSimNoNIC ${PWD}/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.out mkdir -p /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig ln -fs /home/msyksphinz/riscv64//riscv64-unknown-elf/share/riscv-tests/benchmarks/dhrystone.riscv /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv cd /home/msyksphinz/work/firesim/sim/generated-src/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/ && \ ./VFireSimNoNIC /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv +sample=/home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.sample +max-cycles=100000000 +mm_relaxFunctionalModel=0 +mm_writeMaxReqs=16 +mm_readMaxReqs=16 +mm_writeLatency=30 +mm_readLatency=30 +dramsim \ 3>&1 1>&2 2>&3 | /home/msyksphinz/riscv64/bin/spike-dasm > /home/msyksphinz/work/firesim/sim/output/f1/FireSimNoNIC-FireSimRocketChipConfig-FireSimConfig/dhrystone.riscv.out && echo $PIPESTATUS # [ $PIPESTATUS -eq 0 ] Microseconds for one run through Dhrystone: 469 Dhrystones per Second: 2128 mcycle = 234976 minstret = 196530

うーん、最後のステータスが表示されないみたいだ。これはVerilatorのみの問題かなあ?調査する必要があるかもしれない。