Rocketコアをカスタマイズし、FireSimのプラットフォームに乗せ、さらにFPGA合成したAGFIまで作成した。いよいよf1インスタンス上で動作させ、ベンチマークプログラムを動かす。

このとき、前章で紹介したようにFireSim上でBuildrootを立ち上げLinuxにログインした上でベンチマークプログラムを動かしてもよいのだが、これにはいろいろ問題がある。

まず、Buildrootのファイルシステムにどうやってコンパイル済みのベンチマークプログラムを配置するのかだが、一般的には様々な方法がある。例えばwgetコマンドで外部サーバからコンパイル済みのバイナリをダウンロードするして実行することもできるかもしれないが、残念ながらFireSim上で動いているBuildrootはネットワークの設定がされておらず、外部のインターネットに接続することができなかった。

今回はLinuxを立ち上げてベンチマークを動かす方法は諦める。その代わり、FireSimが提供している「ワークロード」というシステムを使う。

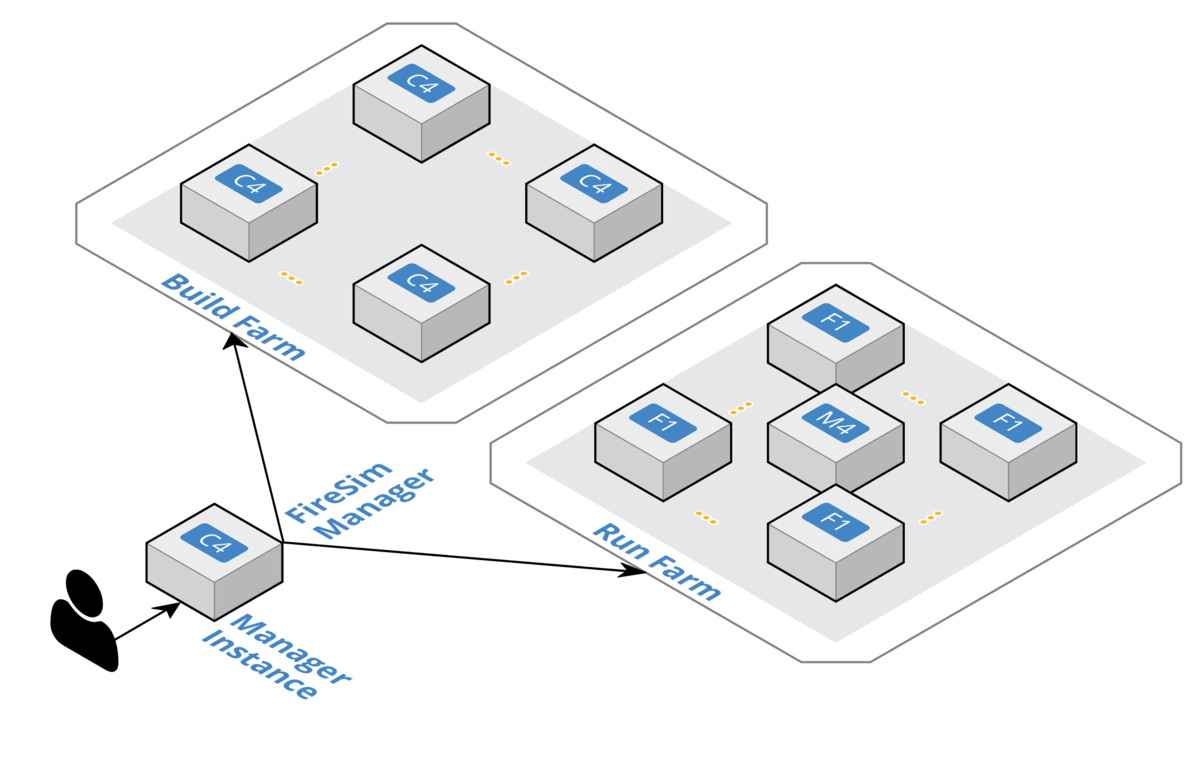

「ワークロード」は、FireSimがターゲットのコンフィグレーションをFPGAに流し込み、そして指定のプログラムをRISC-Vコアに流し込んで結果を回収するための仕組み。 FireSimのベンチマークやリグレッションテストも、このワークロードを使って実行されている。

ここでは、前章で作成したmatrixmulプログラムをAGFI firesim-singlecore-no-nic-matrixmulで動かして結果を回収するために、matrixmulワークロードを作成してみる。

新しいワークロードを定義するためにはdeploy/workloads/matrixmul.iniを作成する。中身はリスト[refs:firesim_workload_matrixmul.ini]のようにする。

リスト[refs:firesim_workload_matrixmul.ini] : deploy/workloads/matrixmul.ini

[runfarm] runfarmtag=matrixmul-unifarm f1_16xlarges=0 m4_16xlarges=0 f1_4xlarges=0 f1_2xlarges=1 runinstancemarket=ondemand spotinterruptionbehavior=terminate spotmaxprice=ondemand [targetconfig] topology=no_net_config no_net_num_nodes=1 linklatency=6405 switchinglatency=10 netbandwidth=200 profileinterval=-1 # This references a section from config_hwconfigs.ini # In homogeneous configurations, use this to set the hardware config deployed # for all simulators defaulthwconfig=firesim-singlecore-no-nic-matrixmul [tracing] enable=no startcycle=0 endcycle=-1 [workload] workloadname=matrixmul.json terminateoncompletion=no

defaulthwconfigに、先ほど作成したfiresim-singlecore-no-nic-matrixmulを指定する。

使用するf1インスタンスはf1_2xlargeなので、f1_2xlarges=1を指定する。さらに、ワークロードとして前章で私用したベンチマークプログラムを使いたいので、ベンチマークの詳細を指定するためのmatrixmul.jsonを作成する。このファイルはworkloadnameで設定する。

次に、matixmul.jsonを作成しましょう。リスト[refs:firesim_workload_matrixmul.json]に、matrixmul.jsonを示す。

リスト[refs:firesim_workload_matrixmul.json] : deploy/workloads/matrixmul.ini

{

"benchmark_name" : "matrixmul",

"common_rootfs" : "dummy.ext2",

"deliver_dir" : "matrixmul",

"common_args" : ["--copies 1"],

"common_files" : ["intrate.sh"],

"common_outputs" : ["/output"],

"common_simulation_outputs" : ["uartlog"],

"workloads" : [

{

"name": "matrixmul.riscv",

"bootbinary" : "matrixmul.riscv",

"simulation_outputs": [],

"outputs": []

}

]

}

ワークロードとしてmatrixmul.riscvを指定した。

このワークロードを実行すると、1つのベンチマークプログラムmarixmul.riscvがFireSimに流し込まれ、その結果が回収される。

次に、matrixmulのワークロードに必要なディレクトリを作成する。

deliver_dirに指定したように、matrixmulディレクトリを作成し、そこに流したいパタンとダミーのファイルシステムを置いておく必要がある。

# firesim/deploy/workloads で作業 mkdir matrixmul cd matrixmul cp ../check-rtc/dummy.ext2 . # target-design/firechip-msyksphinz/tests/ 以下でmakeを実行し、あらかじめmatrixmul.riscvを作成しておいてくこと。 ln -s ../../../target-design/firechip-msyksphinz/tests/matrixmul.riscv

これで準備は完了。FireSimを立ち上げる。

# firesim/deployディレクトリ上で作業をすること。別のディレクトリで実行するとiniとjsonファイルのパスが合わずエラーとなった。 cd firesim/deploy workloads/run-workload.sh workloads/matrixmul.ini --withlaunch

f1インスタンスが立ち上がり、FireSimのデザインが流し込まる。 シミュレーションが開始され、しばらく待っているとコンソールが戻ってくる。 ログが生成されるので確認してみる。

less /home/centos/firesim-msyksphinz/deploy/logs/[実行した日付]-launchrunfarm-B8G7C0DQNCNB0OF0.log

...

2019-05-11 02:45:59,050 [run_workload] [DEBUG] jobs complete dict {u'matrixmul.riscv': True}

2019-05-11 02:45:59,050 [run_workload] [DEBUG] global status: [True]

2019-05-11 02:45:59,050 [run_workload] [INFO ] FireSim Simulation Exited Successfully. See results in:

/home/centos/firesim-msyksphinz/deploy/results-workload/2019-05-11--02-44-10-matrixmul/

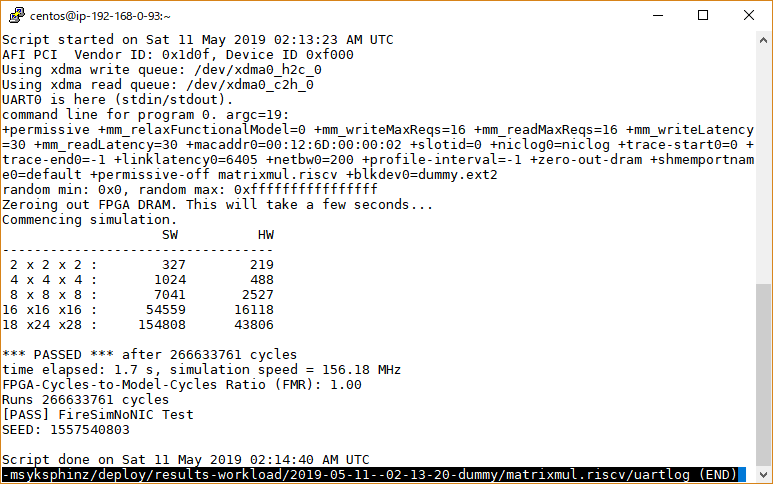

さらに、uartlogを確認してみる。

less /home/centos/firesim-msyksphinz/deploy/results-workload/2019-05-11--02-44-10-matrixmul/matrixmul.riscv/uartlog

Script started on Sat 11 May 2019 02:44:13 AM UTC

AFI PCI Vendor ID: 0x1d0f, Device ID 0xf000

Using xdma write queue: /dev/xdma0_h2c_0

Using xdma read queue: /dev/xdma0_c2h_0

UART0 is here (stdin/stdout).

command line for program 0. argc=19:

+permissive +mm_relaxFunctionalModel=0 +mm_writeMaxReqs=16 +mm_readMaxReqs=16 +mm_writeLatency=30 +mm_readLatency=30 +macaddr0=00:12:6D:00:00:02 +slotid=0 +niclog0=niclog +trace-start0=0 +trace-end0=-1 +linklatency0=6405 +netbw0=200 +profile-interval=-1 +zero-out-dram +shmemportname0=default +permissive-off matrixmul.riscv +blkdev0=dummy.ext2

random min: 0x0, random max: 0xffffffffffffffff

Zeroing out FPGA DRAM. This will take a few seconds...

Commencing simulation.

SW HW

----------------------------------

2 x 2 x 2 : 327 219

4 x 4 x 4 : 1024 488

8 x 8 x 8 : 7041 2527

16 x16 x16 : 54559 16118

18 x24 x28 : 154583 44362

*** PASSED *** after 3913301296 cycles

time elapsed: 25.0 s, simulation speed = 156.26 MHz

FPGA-Cycles-to-Model-Cycles Ratio (FMR): 1.00

Runs 3913301296 cycles

[PASS] FireSimNoNIC Test

SEED: 1557542653

パタンが通り、シミュレーションが終了したのを確認できた(ちなみにデバッグモードにすると、SW実行した場合とHW実行した場合の結果が一致しているのも確認できる。