前回に、Vivado-HLSで作成した浮動小数点行列積回路をAXI4-Streamに対応させた。今度はVivado側で、作成したIPをDMAに接続して、デザインを作成してみよう。

参考にしたのは、例によって以下の資料だ。

http://japan.xilinx.com/support/documentation/application_notes/j_xapp1170-zynq-hls.pdf

この資料では、作成したIPをDMAで接続している。さらに接続の詳細については振れられず、スクリプトを使って自動的に接続するように構成されていた。 従って、以下の資料をダウンロードして参照すると手っ取り早いのだと思われる。

https://secure.xilinx.com/webreg/clickthrough.do?cid=343614

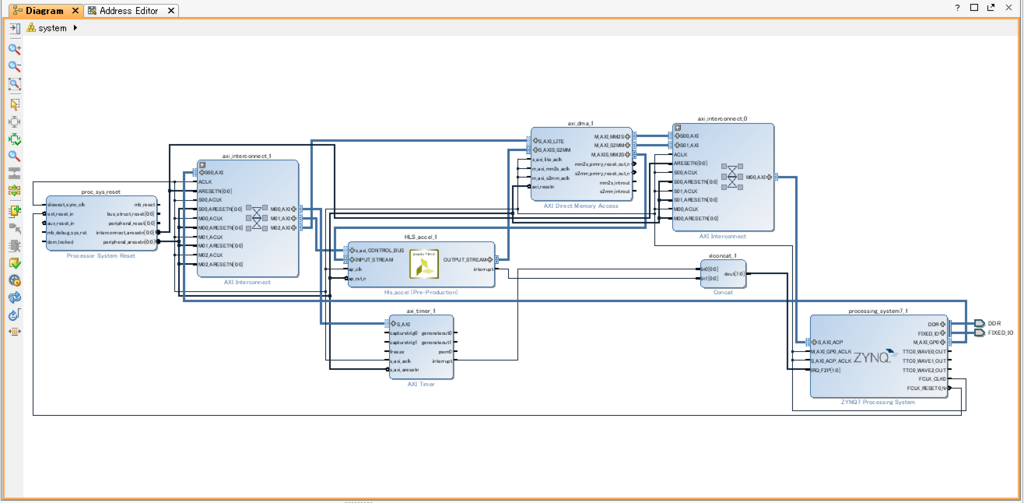

以下のようなデザインが作成されている。接続されているのは、作成したカスタムIPと、AXI4-DMA、さらにAXIタイマーが接続されている。 どうやらこのタイマーを使って何かを制御するらしい。ソースコードを参照した限り、このタイマーはサイクル数を計測するのに利用する感じがしている。 今回僕のデザインでは、ARM側で計測するのでこれは必要ない、はず。

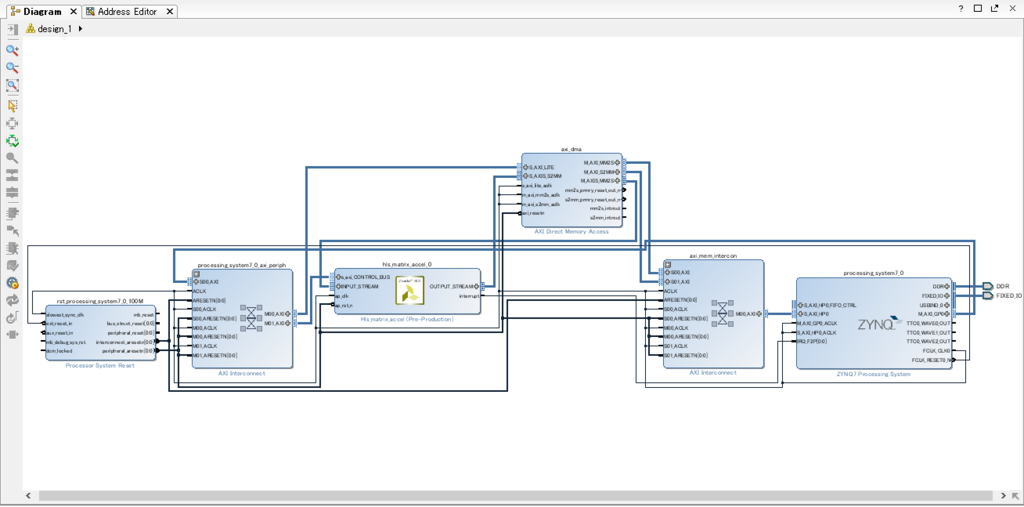

僕の場合は以下のようなデザインを構築した。

リファレンスデザインと非常に似ている。違っているのはタイマーを利用していないくらいだ。

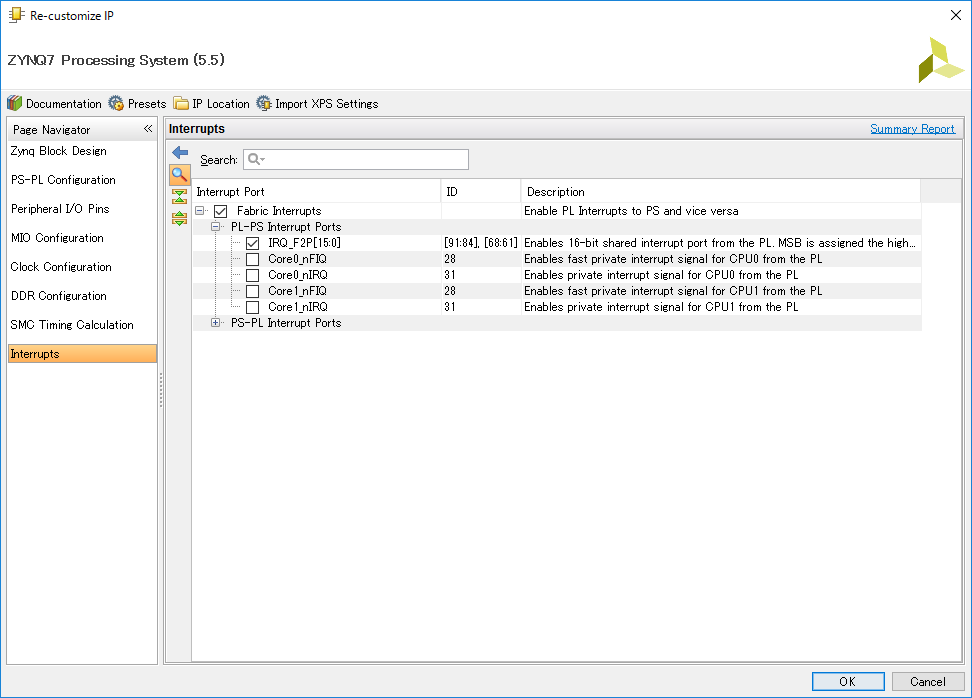

割り込みを利用したいので、ProcessingSystemで汎用割り込みポートを有効にしている。

割り込みポートは1つだけ用意している。僕のデザインの場合はaxi_timerを利用しないため、2つの割り込みをconcatする必要が無いため、xlconcatモジュールは使用していない。

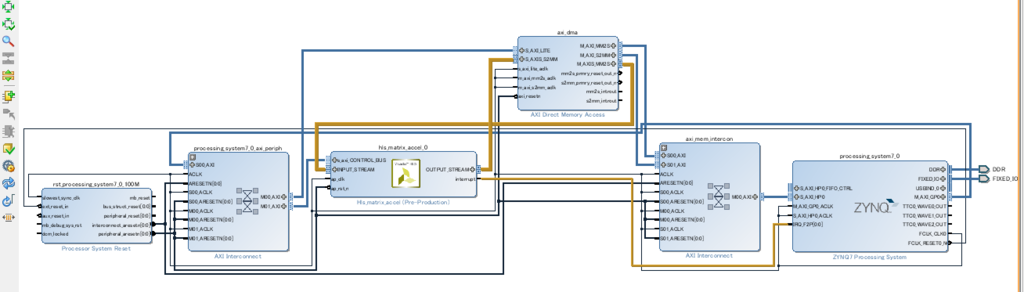

また、以下で強調表示したポートは手動で接続した。どうやら、Autoではうまい具合に接続してくれないらしい。

これで合成して、次にSDKを使ってプログラムを書いていく。