非常に荒削りだが、chip-architect.com の"Understanding the detailed Architecture of AMD's 64bit Core"の第1章にあたる、"The Integer Core"の翻訳を終了した。

オリジナルの文章はこちら。

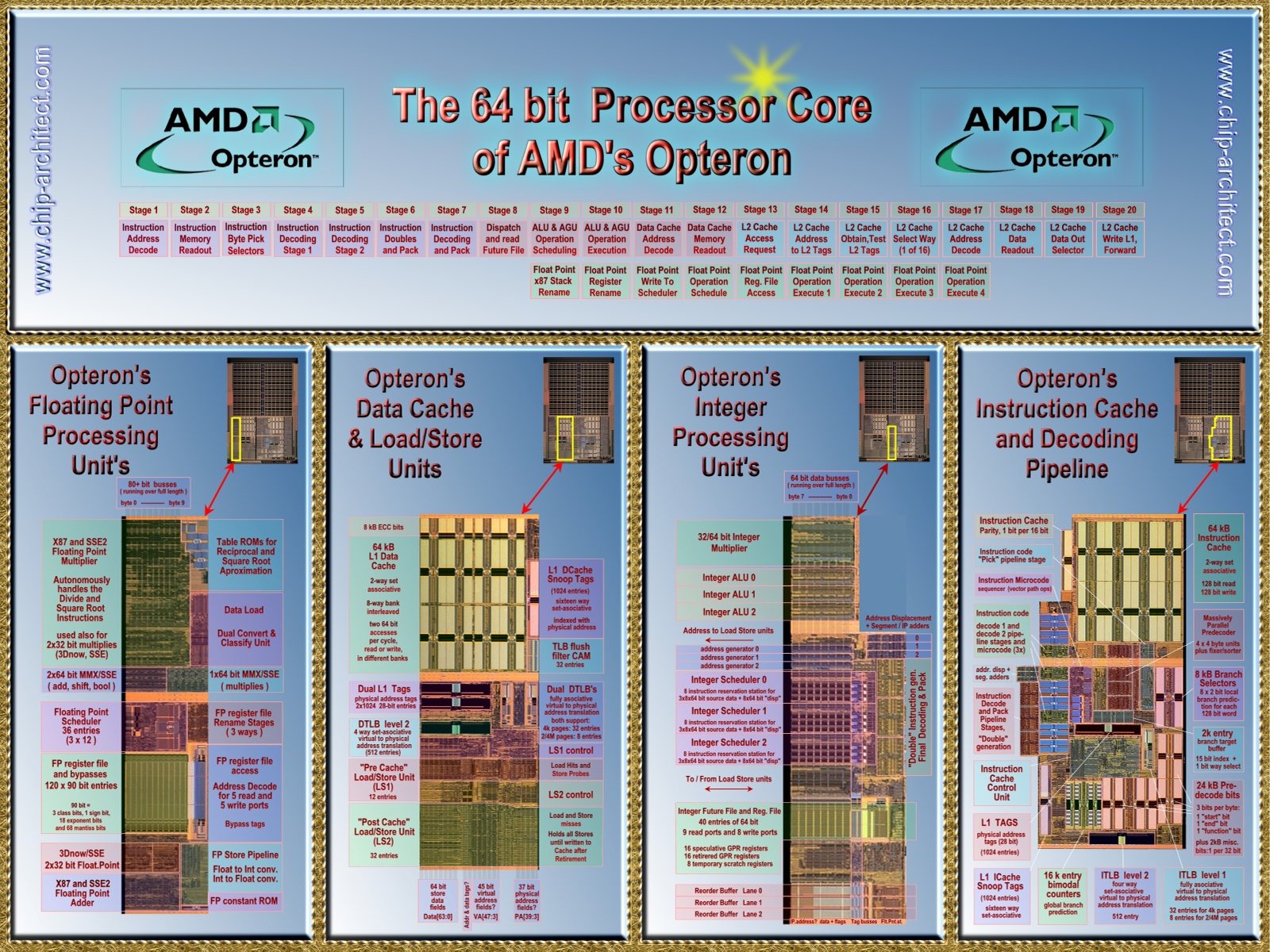

Chip Architect: Detailed Architecture of AMD's Opteron

翻訳の文章はこちら。

プロセッサの設計者であったり、コンピュータアーキテクチャん興味がある人だったら、楽しく読める解説記事なのではないかと思う。かなり古い文章だけれども、スーパスケーラプロセッサの基礎になる部分が含まれている。

スケジューリングから実行までに必要なサイクル数をなるべく減らしていくということ

Opteronを例に取っているのだが、例えばリザベーションステーションで前の命令の結果を待ち合わせているときに、1サイクルでも次の命令を速く発行できるように、結果を取得する1サイクル前にタグを出力する。 タグを監視しているリザベーションステーションは、一致するタグが流れてきた時点で命令を発行してしまう。データの到着は後でも良いという訳だ。 これにより、リザベーションステーションでデータを待ち合わせるのではなく、ALU内でデータが到着することが分かった時点で命令が発行されるようになり、発行までの時間を早めることができる。

まあこれは現在のプロセッサにとってはかなり常識的なことかもしれないけど、こういう1サイクルを削り取る努力により、アーキテクチャというのは進化していくのだなあと思う。

アーキテクチャだけでない、動作周波数を上げるための回路の単純化

例えば、リオーダバッファを1つのレジスタファイルで作ってしまうと、読み出しポートと書き込みポートが莫大必要になり、巨大な回路を生成&動作周波数が低下してしまう。 これを解決するために、最初から同時命令発行数の最大値が3なのであれば、リオーダバッファを3つに分割し、その中でデータのやりとりをする。 これにより、読み出しと書き込みのポート数を各リオーダバッファで1つに抑えることができ、回路の単純化に繋がる。

アーキテクチャの改善には、動作周波数を上げるための様々な単純化が必要になる。単純さを維持しつつ、アーキテクチャとしても性能を維持しなければならないというのが、プロセッサアーキテクトの腕の見せ所なんだよなあ(とても大変だけれども)。