Ubuntu16.04 (xenial) で作業をしているのだが、Virtual Boxを立ち上げてPuttyからXを飛ばしてEmacsを立ち上げたりすると、フォントが異常に読みにくいことがある。

これは非常に嫌なので僕がWindowsの普段使いしているSource Han Code JP(源ノ角ゴシック)を導入しよう。

UbuntuへのSource Han Codeのインストール

基本的にググればすぐに出てくるので問題ない。

- Adobe Font Development Kitのダウンロード

Adobe - Adobe Font Development Kit for OpenType | Adobe Developer Connection

「Agree and download FDK-2.5.65463-LINUX.zip (ZIP, 32.6 M)」をダウンロードして展開しておく。

wget http://download.macromedia.com/pub/developer/opentype/FDK.2.5.65463/FDK.2.5.65463-LINUX.zip

unzip FDK.2.5.65463-LINUX.zip

cd FDK/

sudo ./FinishInstallLinux

一度ターミナルをログアウトして再ログインする。

$ sudo ./FinishInstallLinux

Adding a symbolic link from '/home/masayuki/bin' to the FDK directory /home/masayuki/work/FDK.

Adding a command to your login file that will append the FDK path to the $PATH environment variable...

I added some lines to the startup file /home/masayuki/.profile for the bash/sh/zsh versions of the Terminal program, in order to add the 'FDK/Tools/linux' directory to your PATH environment variable.

Changed to file /home/masayuki/.profile

If you cannot run the FDK tools by name from the command-line after logging out and then back in, then your

Terminal program may be using a different login file than the ones I modified.

If so, you will need to identify your login file, and then add the same two lines to that file.

You must log out, and log back in, before the changes will take effect.

The FDK will then be ready to use.

- Source Han Code JPのダウンロードとインストール

こちらはGithubからダウンロードしてくる。

git clone https://github.com/adobe-fonts/source-han-code-jp

cd source-han-code-jp

sh ./commands.sh

cp ./*/*.otf ~/.fonts/ # ~/.fontsがない場合は自分で作った。

sudo fc-cache -fv

インストールに失敗する場合は、いくつかPythonのパッケージを確認すること。

sudo apt-get install gcc-multilib g++-multilib

sudo aptitude install python-pip

sudo pip install fonttools

これで、フォントがインストールされていることが確認できる。fc-listsで確認してみよう。

$ fc-list | grep Han

/home/masayuki/.fonts/SourceHanCodeJP-HeavyIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP H It,源ノ角ゴシック Code JP H It:style=H It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-Light.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP L,源ノ角ゴシック Code JP L:style=L,Regular

/home/masayuki/.fonts/SourceHanCodeJP-Regular.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP R,源ノ角ゴシック Code JP R:style=R,Regular

/home/masayuki/.fonts/SourceHanCodeJP-ExtraLightIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP EL It,源ノ角ゴシック Code JP EL It:style=EL It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-NormalIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP N It,源ノ角ゴシック Code JP N It:style=N It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-MediumIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP M It,源ノ角ゴシック Code JP M It:style=M It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-ExtraLight.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP EL,源ノ角ゴシック Code JP EL:style=EL,Regular

/home/masayuki/.fonts/SourceHanCodeJP-Heavy.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP H,源ノ角ゴシック Code JP H:style=H,Regular

/home/masayuki/.fonts/SourceHanCodeJP-Bold.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP B,源ノ角ゴシック Code JP B:style=B,Regular

/home/masayuki/.fonts/SourceHanCodeJP-BoldIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP B It,源ノ角ゴシック Code JP B It:style=B It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-Medium.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP M,源ノ角ゴシック Code JP M:style=M,Regular

/home/masayuki/.fonts/SourceHanCodeJP-LightIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP L It,源ノ角ゴシック Code JP L It:style=L It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-RegularIt.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP R It,源ノ角ゴシック Code JP R It:style=R It,Regular

/home/masayuki/.fonts/SourceHanCodeJP-Normal.otf: 源ノ角ゴシック Code JP,Source Han Code JP,Source Han Code JP N,源ノ角ゴシック Code JP N:style=N,Regular

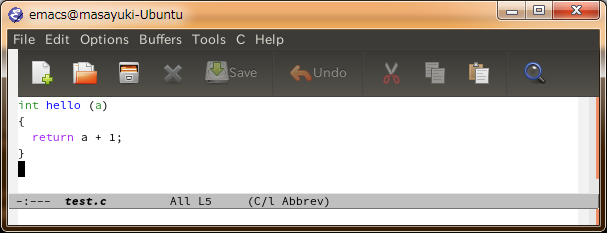

いろいろ試行錯誤したのだが、やっぱり~/.emacs/init.elに以下を追加するのがシンプルだ。

(set-default-font "Source Han Code JP N")

きれいなフォントになった!