ヘネシー先生だ!(iPhoneで撮ったので画質が非常にイマイチである)

慶應義塾大学にて、大川賞という情報通信技術に関する顕著な成果、また研究教育について顕著な成果を上げた方に対する表彰の、記念講演が行われた。 今年の受賞者は「ヘネパタ」でおなじみのJohn.L.Hennessy先生と、日本における最初のトランジスタコンピュータ開発に携わった相磯秀夫先生だった。

相磯先生はもちろん、ヘネシー先生といえば学生のころから「ヘネパタ」「パタヘネ」「MIPS」などの分野で常にかかわってきた大先生だ。 これはもう聞きに行かなければ、ということで早速記念講演を聴いてきた。 場所は慶應義塾大学の日吉キャンパスだ。

ちなみに、講演内容は以下で視聴可能となっている。

John.L.Hennessy先生 「The End of Road for General Purpose Processors and the Future of Computing」

タイトルから分かるとおり、"The End of Road for General Purpose Processors」なのだ。 ヘネシー先生はこれまでの汎用プロセッサに関するRISCの重要性、例えばILPの向上やマルチプロセッサなどの、性能向上のためにさまざまなアプローチを取った歴史を振り返りつつ、これ以上の進化は望めないという考え方を示されたようにも思える(これはあくまでも私の主観)。

時代とともにコンピュータにとって重要な分野は変わっており、かつては高い命令レベル並列性、そしてマルチプロセッサ並列性、そして現状ではモバイルプロセッサにおけるバッテリーにの持ちを重視するための、消費電力へと焦点が移っている。 そして最終的にはプロセッサのこれ以上の性能向上を望むのは難しいとする(たとえマルチプロセッサの数を増やしたとしても)見解を示し、DSA(Domain Specific Architecture)への発展が重要ということでまとめられた。 これは例えばGPGPUの進化だったり、VR向けのプロセッサ、果てはAI向けにTensorFlow専用のプロセッサのことだったりするのだろう。

つまり、汎用プロセッサにとってこれ以上の進化は望めない、ということではなかろうか。 少なくとも研究対象としての魅力度は確実に下がっている、ということだろう。

汎用プロセッサが消滅することはないだろう。DSAがいくら進化したところで、じゃあOSは誰が動かすの?DSAのデバイスを誰が制御するの?という話になる。DSAだけ速くても駄目なのだ。

また、いくらDSAが進化したところで、ASICチップを作るのに数億円かかるこの時代である。特定向けのアプリケーションプロセッサを、大量に作るなんて、そんなの現実的には不可能だ。

ASICチップを大量に作るためには何が必要か?それは大企業のような体力のあるところ、例えばGoogleやAmazonのような人材と体力のある組織しか作ることは出来なくなるだろう。

ミニマルファブはどうか?コストは低いが性能はイマイチ、しかしここは高性能な汎用プロセッサとのトレードオフとなる。いくら専用チップを作っても、先端プロセスで作れなければ、汎用プロセッサを使ったほうがマシ、という事だってあり得る。

先端プロセスでなくても、専用ハードでDSAを作れば性能的に太刀打ちできるだって?じゃあDSA向けのソフトウェアとプラットフォームは誰が作るんだい?エコシステムを構築する労力は想像を絶するものだ。それなら多少性能的に劣っていても汎用プロセッサを使ったほうが楽ということになる。

話を戻すが、もはやDSAをアプリケーション毎に作ることの出来る体力を持っている日本企業は存在せず、海外の垂直統合している、体力のある組織しか作ることが出来なくなる。

そう考えると、ヘネシー先生の見解は決して絶対的なものではなく、ただ単に「時代は繰り返す」というか、「汎用」→「専用」→「汎用」のループはこれからも続くよ、ということを示しただけにも思える。

相磯秀夫先生 「コンピュータサイエンス関連分野における研究・教育の体験~コンピュータアーキテクチャの研究から大学改革まで~」

相磯先生の言葉の節々からは非常に謙虚な印象が感じ取れるが、やっていることは非常に最先端であったことだろう。

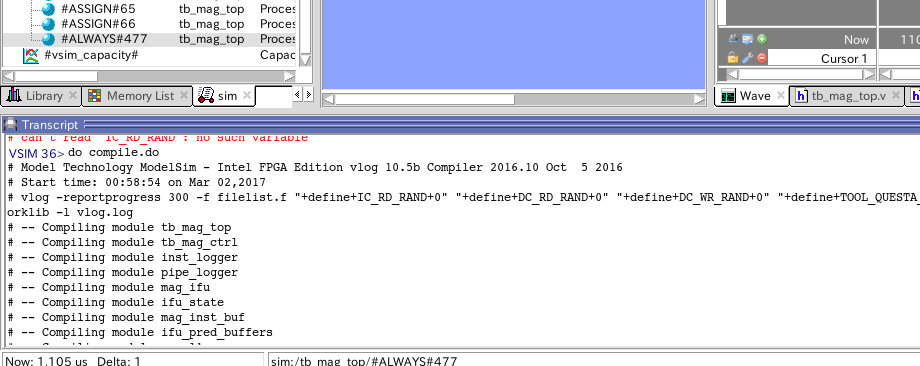

今でこそ僕たちはすでにあるプラットフォーム上でVerilogを書いたり、チップを作ったりしているが、全く存在しないデバイスや、どうやったらいいのか全く分からない新しい技術を始めるのは相当な苦労であることは想像できる。

日本で始めてのトランジスタコンピュータを作るというのは非常に難しい挑戦だったと思うし、デジタル回路の設計だけでなく、パッケージや安定性についても考えなければならない。 そのためには、垂直にすべてのことが分かるエンジニアが必要になるというわけだ。

午後のディスカッションでも話題になっていたが、ヘネシー先生のスタンフォードでは、「T字型」の人材を作ることを目標としているらしい。 T字というのは、幅広い分野の知識を持っているが、ひとつの分野に対しては非常にエキスパートということを意味している。 もはや水平分業では、イノベーションを起こすのは難しいという見解は両者とも一致していた。

相磯先生の興味分野はやはり学生の教育についてであり、その点で非常に熱く語られていた。

まずは学生の自主性を尊重すること、また修士課程においては自分で課題を発見し、それを解決することが重要視されること言うことを言われていた。 これは僕が大学院に在籍していた研究室でもそうだったが、自分で課題を発見するというのは意外と難しいことなので、それだけでも訓練になる。

また、海外の国際学会で積極的に発表するということも重要視していたらしい。 海外で発表して帰ってきた学生は、目の色が違っており、博士に進みたいと言い出す学生もたくさんいるとおっしゃっていたが、まあここについては眉唾ものだろう(笑)。

海外に出る学生が少なくなったと言うことだが、パネルディスカッションで両先生が指摘していたとおり、海外に行かずとも良い環境で勉強が出来るようになったこと、インターネットの発展で、日本にいても十分なべんきょうが出来るようになったことが挙げられる。

ただし、僕が思うにやはり国内と海外では学生の質も異なるだろうし(日本の学生が勉強しないという訳では無いし、海外の学生がめっちゃ勉強するという訳でもないだろうが)、海外に出る、という手段ばかり考えるのではなく、なんのために海外に出るのか(より厳しい環境に身をおく、とか)を考えたほうが、学生にとってより有意義な海外生活を送ることが出来るのではなかろうか(僕は留学経験は無いけれども)。