OpenSPARC T1のコア部分のみを切り出したものとして、S-RISC (Simply-RISC)というものをコメントで紹介してもらった。

どうやら、コアの部分をOpenSPARC-T1として利用し、それ以外の外側を独自に囲むことによってOpenSPARCを動作させるものらしい。 概要図を当該HPから引用する。

上記のとおり、OpenSPARC-T1のコアはそのまま利用し、外部へのWishboneバスおよびペリフェラルを追加することによって動作させる仕組みだ。

With this new system, now Linux boots correctly as single-thread! And even using PROM file 1c4t_obp_prom.bin, i.e. the four-threads version of the OpenBoot code, Linux starts booting.

どうやらシングルコアでもLinuxのブートに成功しているらしい。すごいな!

という訳で早速チャレンジしてみることにする。

S1 Coreのダウンロードとインストール

以下からS1 Coreのダウンロードを行う。解答するとsourcemeというファイルが見えるので、これを編集する。

# General paths settings export S1_ROOT=~/work/s1_core export T1_ROOT=~/work/opensparc/t1 export PATH=.:$S1_ROOT/tools/bin:$PATH

まず、OpenSPARC T1のソースコードはダウンロードしていること(http://www.oracle.com/technetwork/systems/opensparc/opensparc-t1-page-1444609.html)が必要である。

コア部分はOpenSPARCそのものを利用しているということになる (これはT1_ROOT変数にて指定されている)。

そして、ダウンロードしたS1 Coreの場所を指定している (これはS1_ROOT変数にて指定されている)。

sourcemeを読み込んで、update_filelistによりファイルリストが更新される。

source sourceme

update_filelist

Icarus Verilogによるシミュレーション環境構築

シェル一覧を見ていると、どうやらVcs, Icarus Verilogでの動作をサポートしているらしい。Vcsなんて持っていないので、Icarus Verilogでシミュレーションしてみよう。

build_icarus run_icarus

しばらくするとシミュレーションが完了する。vcdファイルが生成されたようだ。

$ run_icarus

Simulation completed!

To see the output:

less /home/xxx/work/s1_core/run/sim/icarus/sim.log

Too watch the waveforms:

gtkwave /home/xxx/work/s1_core/run/sim/icarus/trace.vcd

vcdを眺めるのは面倒だし、ちょうどModelSimをインストールしているのでwlf形式に変換した。

vcd2wlf trace.vcd trace.wlf

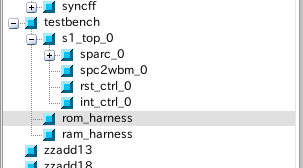

ModelSimで波形を開いてみた。構造としてはS1コアの横に命令ROM、データROMが接続されているような状態だ。 命令ROMの波形を出してみると、ちゃんとフェッチが効いているようなので、これは動作しているのかな?もうちょっと掘り下げてみよう。