前回、SiFiveのFreedomプラットフォームについてまとめたが、今回は実際にそのプロジェクトを触ってみる。

Freedomプラットフォームはgithubに公開されており、デバイスさえあれば誰でもビルドすることができるようになっている。

ビルド対象のFPGAは2種類用意されており、Freedom EverywhereではDigilentのArty FPGA、Freedom UnleashedではXilinxのVC707 FPGA Boardをターゲットとしている。

とりあえずWebPackを持っている私としては、DigilentのArty FPGAボードのほうが入手しやすい(持ってないけど)。 どのようなプロジェクトが出来上がるのか、確認しておこう。

Vivado WebPackでFreedom E310 Arty FPGA Dev Kitをビルドするためには

Vivado WebPackはデフォルトではArty FPGAボードの情報を持っていない。したがって、VivadoをインストールしてすぐにArty向けにビルドをしてもエラーをはいて終了してしまう。

そこで、DigilentのホームページからArty FPGAボードのボード情報ファイルを取得してきた。

Vivado Version 2015.1 and Later Board File Installation [Reference.Digilentinc]

“Download"からボード情報をダウンロードして、展開した。これをXilinxのVivadoインストールフォルダの/data/boards/board_filesに展開する。

上手く行けば、VivadoのCreate Projectから、Artyボードを選択できるようになっているはずだ。

これを確認して、SiFiveプラットフォームをビルドしてみる。

$ make -f Makefile.e300artydevkit verilog $ make -f Makefile.e300artydevkit mcs

無事にビルドが完了し、FPGA用のMCSファイルが生成されると、以下のようなメッセージとともにVivadoが終了する。

...

# create_fileset -simset sim_1

# }

# set obj [current_fileset -simset]

# add_files -norecurse -fileset $obj [glob -directory $srcdir {*.v}]

# set_property TOP {tb} $obj

# if {[get_filesets -quiet constrs_1] eq ""} {

# create_fileset -constrset constrs_1

# }

# set obj [current_fileset -constrset]

# add_files -norecurse -fileset $obj [glob -directory $constrsdir {*.xdc}]

source script/cfgmem.tcl

# lassign $argv mcsfile bitfile datafile

# set iface spix4

# set size 16

# set bitaddr 0x0

# write_cfgmem -format mcs -interface $iface -size $size \

# -loadbit "up ${bitaddr} ${bitfile}" \

# -loaddata [expr {$datafile ne "" ? "up 0x400000 ${datafile}" : ""}] \

# -file $mcsfile -force

Command: write_cfgmem -format mcs -interface spix4 -size 16 -loadbit {up 0x0 obj/system.bit} -loaddata {} -file obj/system.mcs -force

Creating config memory files...

Creating bitstream load up from address 0x00000000

Loading bitfile obj/system.bit

Writing file obj/system.mcs

Writing log file obj/system.prm

===================================

Configuration Memory information

===================================

File Format MCS

Interface SPIX4

Size 16M

Start Address 0x00000000

End Address 0x00FFFFFF

Addr1 Addr2 Date File(s)

0x00000000 0x0021728B Mar 28 23:45:11 2017 obj/system.bit

0 Infos, 0 Warnings, 0 Critical Warnings and 0 Errors encountered.

write_cfgmem completed successfully

INFO: [Common 17-206] Exiting Vivado at Tue Mar 28 23:45:45 2017...

make[1]: Leaving directory '/home/msyksphinz/work/freedom/fpga/e300artydevkit'

cp /home/msyksphinz/work/freedom/fpga/e300artydevkit/obj/system.mcs /home/msyksphinz/work/freedom/builds/e300artydevkit/sifive.freedom.everywhere.e300artydevkit.E300ArtyDevKitConfig.mcs

dcp(Design Check Point)が生成されていたので、ちょっと見てみた。

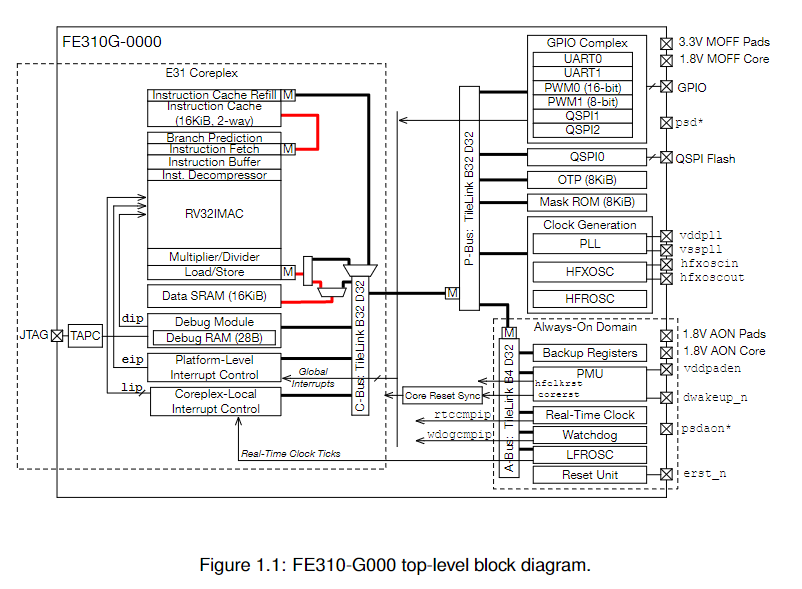

Coreplexが、CPUの部分だ。