LiteXはSoCを半自動的に生成するための総合環境で、自作CPUのSoC生成環境もLiteXを使用している。

LiteXでのFPGA合成環境は情報があまりなく、まとめておきたいと思う。 先ずはサンプルプログラムを動かす。いろいろ調査した結果、以下の環境を利用できる。

まずはこのリポジトリをダウンロードする。

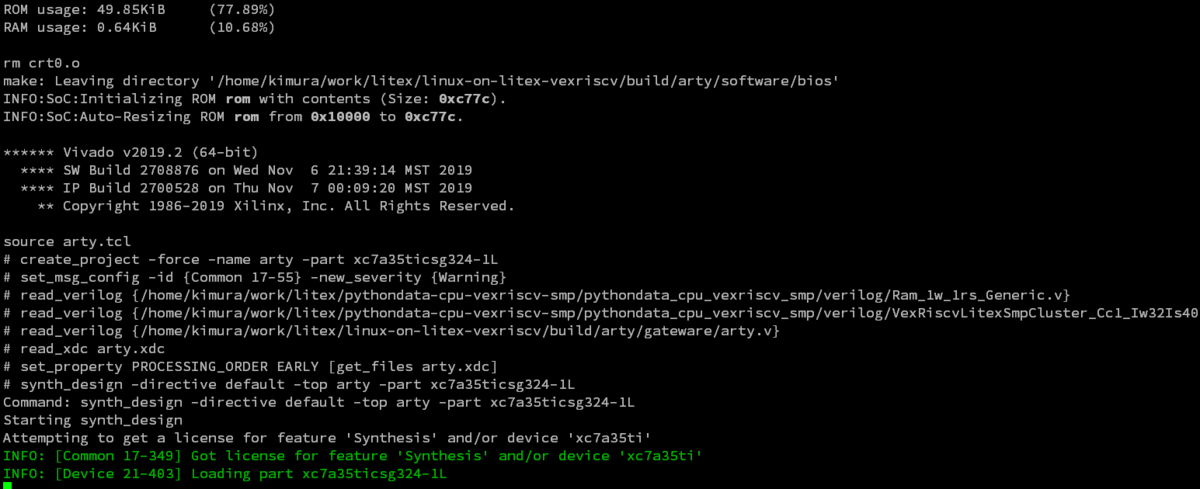

git clone https://github.com/litex-hub/linux-on-litex-vexriscv cd linux-on-litex-vexriscv export LITEX_ENV_VIVADO=/home/msyksphinz/opt/cad/xilinx/Vivado/2019.2 ./make.py --board=arty --cpu-count=1 --build

これだけで論理合成がスタートできる。あまりにもシンプルすぎて何が起きているのかよく分からない。

論理合成結果を確認してみる。一応うまくいっているようだ。

1. Slice Logic -------------- +----------------------------+-------+-------+-----------+-------+ | Site Type | Used | Fixed | Available | Util% | +----------------------------+-------+-------+-----------+-------+ | Slice LUTs | 12084 | 0 | 20800 | 58.10 | | LUT as Logic | 9760 | 0 | 20800 | 46.92 | | LUT as Memory | 2324 | 0 | 9600 | 24.21 | | LUT as Distributed RAM | 2304 | 0 | | | | LUT as Shift Register | 20 | 0 | | | | Slice Registers | 8861 | 0 | 41600 | 21.30 | | Register as Flip Flop | 8861 | 0 | 41600 | 21.30 | | Register as Latch | 0 | 0 | 41600 | 0.00 | | F7 Muxes | 554 | 0 | 16300 | 3.40 | | F8 Muxes | 1 | 0 | 8150 | 0.01 | +----------------------------+-------+-------+-----------+-------+

------------------------------------------------------------------------------------------------

| Design Timing Summary

| ---------------------

------------------------------------------------------------------------------------------------

WNS(ns) TNS(ns) TNS Failing Endpoints TNS Total Endpoints WHS(ns) THS(ns) THS Failing Endpoints THS Total Endpoints WPWS(ns) TPWS(ns) TPWS Failing Endpoints TPWS Total Endpoints

------- ------- --------------------- ------------------- ------- ------- --------------------- ------------------- -------- -------- ---------------------- --------------------

0.085 0.000 0 42769 0.021 0.000 0 42768 0.264 0.000 0 12189