LiteXは自分でSoC環境を構成することができるツール。自作CPUをSoCに組み込んでみたいので、今回はこれを試行してみる。

Rocketでのコンフィグレーションもできるらしい。以下でチェックしてみる。

下記のコマンドで、Rocket用のパッケージをインストールする必要がある。

pip3 install git+https://github.com/litex-hub/pythondata-cpu-rocket.git

litex_sim --cpu-type=rocket

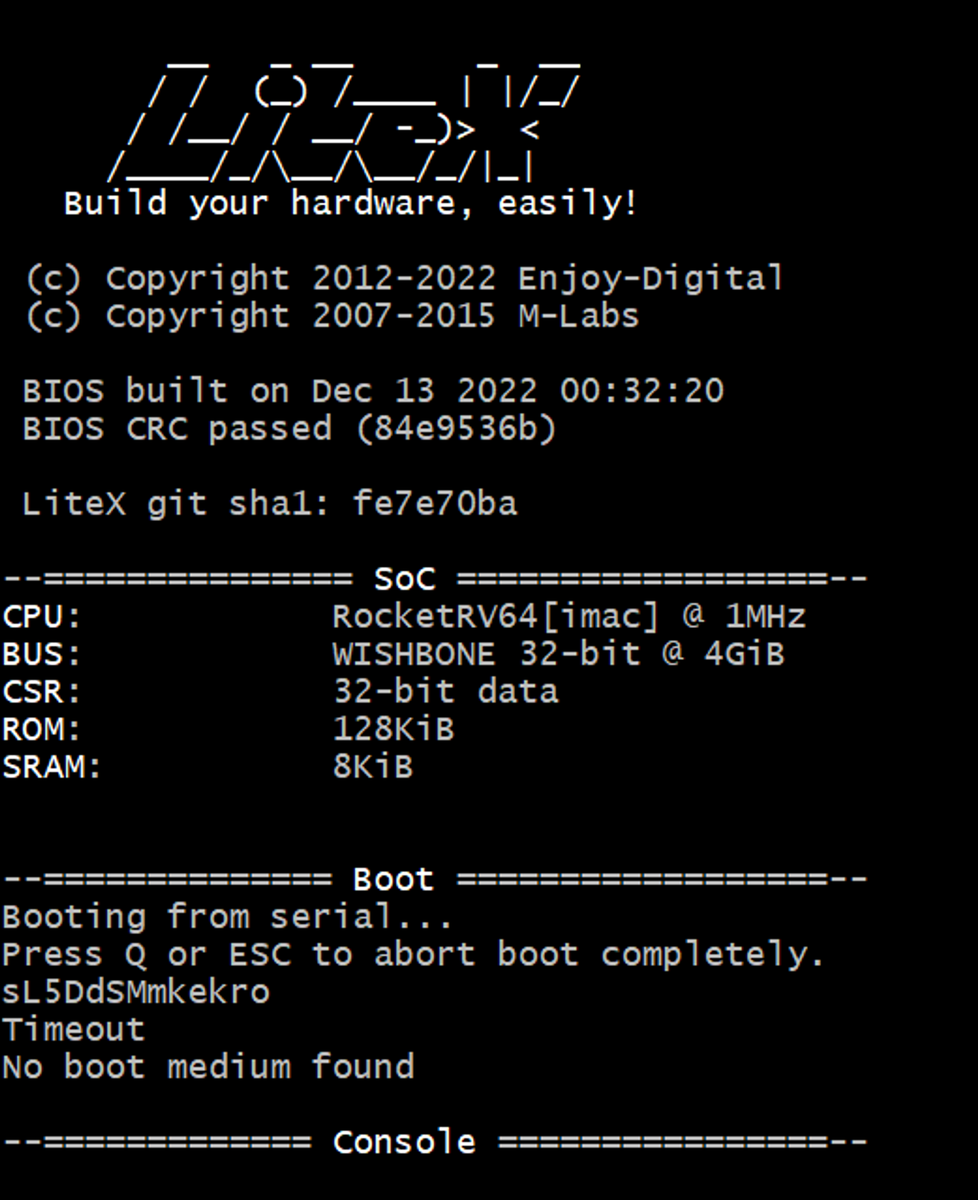

__ _ __ _ __

/ / (_) /____ | |/_/

/ /__/ / __/ -_)> <

/____/_/\__/\__/_/|_|

Build your hardware, easily!

(c) Copyright 2012-2022 Enjoy-Digital

(c) Copyright 2007-2015 M-Labs

BIOS built on Dec 13 2022 00:32:20

BIOS CRC passed (84e9536b)

LiteX git sha1: fe7e70ba

--=============== SoC ==================--

CPU: RocketRV64[imac] @ 1MHz

BUS: WISHBONE 32-bit @ 4GiB

CSR: 32-bit data

ROM: 128KiB

SRAM: 8KiB

--============== Boot ==================--

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

Timeout

No boot medium found

--============= Console ================--

litex>

このコンフィグレーションだが、以下のリポジトリで作成できるらしい。

CPUのvexriscvに必要なPython以外のファイルは、Pythonのライブラリやツールで使用できるように、Pythonモジュールにパッケージ化されています。 これは、LiteXのようなツールで使用する際に便利です。 データファイルはpythondata_cpu_vexriscvというPythonモジュールで見つかります。pythondata_cpu_vexriscv.data_locationの値は、ファイルシステム上でファイルを見つけるために使用することができます。 データファイルを直接取得する例

import pythondata_cpu_vexriscv my_data_file = "abc.txt" with open(os.path.join(pythondata_cpu_vexriscv.data_location, my_data_file)) as f: print(f.read())

これのテンプレートファイルは、以下から入手すればいいらしい。

これを改造してみよう。