LiteXはSoCを半自動的に生成するための総合環境で、自作CPUのSoC生成環境もLiteXを使用している。

前回、自作CPU向けにビルドしたつもりが、VexRiscvをコンパイルしてしまっていた。

これを修正するためには、同時にsoc_linux.pyを修正する必要がある。

diff --git a/soc_linux.py b/soc_linux.py index fa35c066..2b8b867b 100644 --- a/soc_linux.py +++ b/soc_linux.py @@ -13,7 +13,7 @@ from migen import * from litex.soc.interconnect.csr import * -from litex.soc.cores.cpu.vexriscv_smp import VexRiscvSMP +from litex.soc.cores.cpu.scariv import ScariV from litex.soc.cores.gpio import GPIOOut, GPIOIn from litex.soc.cores.spi import SPIMaster from litex.soc.cores.bitbang import I2CMaster @@ -32,8 +32,8 @@ def SoCLinux(soc_cls, **kwargs): # SoC ---------------------------------------------------------------------------------- soc_cls.__init__(self, - cpu_type = "vexriscv_smp", - cpu_variant = "linux", + cpu_type = "scariv", + cpu_variant = "standard", **kwargs) # RGB Led ----------------------------------------------------------------------------------

あと、LiteXはdefine文を制御することはできないのだろうか?

コンフィグレーションによってdefineを挿入したりしなかったりを制御したいのだが、Vivadoのビルドにそれが反映されていない。

これにより、最後までVivadoのビルドが動くようになった。

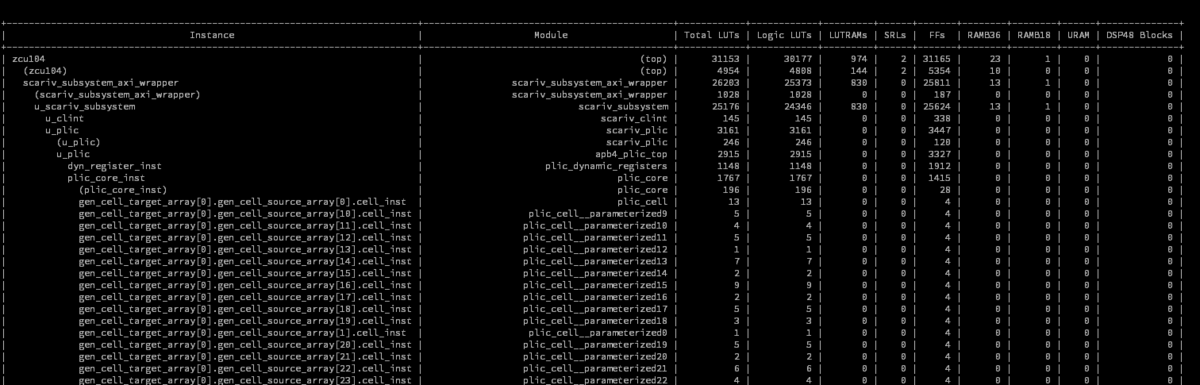

それでも、最後のdtsが生成できない。PLICの生成がうまくいっていないのかな。

write_bitstream completed successfully

write_bitstream: Time (s): cpu = 00:00:28 ; elapsed = 00:00:47 . Memory (MB): peak = 5969.426 ; gain = 0.000 ; free physical = 109567 ; free virtual = 130061

# quit

INFO: [Common 17-206] Exiting Vivado at Mon Mar 27 13:36:02 2023...

Traceback (most recent call last):

File "/home/msyksphinz/work/litex/litex_scariv/./make.py", line 945, in <module>

main()

File "/home/msyksphinz/work/litex/litex_scariv/./make.py", line 921, in main

soc.generate_dts(board_name)

File "/home/msyksphinz/work/litex/litex_scariv/soc_linux.py", line 133, in generate_dts

dts_content = generate_dts(json.load(json_file), polling=False)

File "/home/msyksphinz/work/litex/litex_scariv/litex/tools/litex_json2dts_linux.py", line 310, in generate_dts

plic_base =d["memories"]["plic"]["base"],

KeyError: 'plic'