自作CPUに対して割込みコントローラの実装をしているが、久しぶりに時間ができたのでこれの修正を行っている。

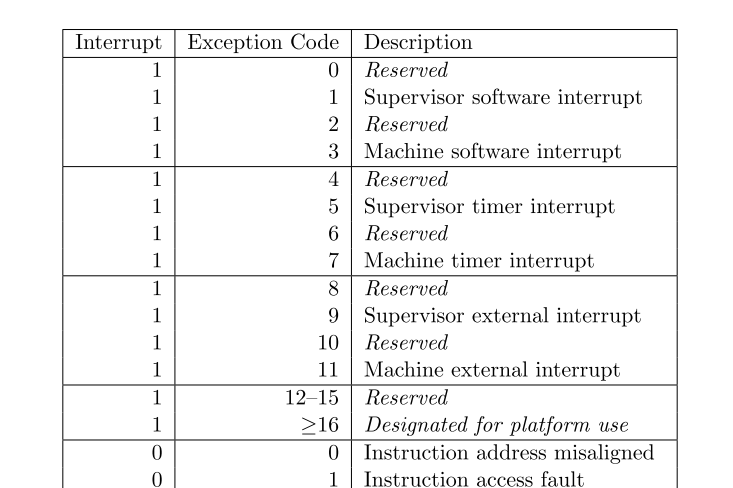

テストで割り込みがかかるようになったのだが、途中でテストがFailしている。問題はmcauseの設定だ。 mcauseは、例外の要因をOne Hotではなくエンコードされた割込み要因の値として格納しなければならない。この機能が抜けていた。

実装としては単純にセレクトを挿入している。とりあえず割込み要因は多くないのでこれで何とかなるかな。

xlen_t deleg_int_encoded; xlen_t int_encoded; assign deleg_int_encoded = (r_mideleg & w_m_int_en) == (1 << riscv_common_pkg::MACHINE_SOFT_INT ) ? riscv_common_pkg::MACHINE_SOFT_INT : (r_mideleg & w_m_int_en) == (1 << riscv_common_pkg::MACHINE_TIMER_INT ) ? riscv_common_pkg::MACHINE_TIMER_INT : (r_mideleg & w_m_int_en) == (1 << riscv_common_pkg::MACHINE_EXTERNAL_INT) ? riscv_common_pkg::MACHINE_EXTERNAL_INT : 'h0; assign int_encoded = w_m_int_en == (1 << riscv_common_pkg::MACHINE_SOFT_INT ) ? riscv_common_pkg::MACHINE_SOFT_INT : w_m_int_en == (1 << riscv_common_pkg::MACHINE_TIMER_INT ) ? riscv_common_pkg::MACHINE_TIMER_INT : w_m_int_en == (1 << riscv_common_pkg::MACHINE_EXTERNAL_INT) ? riscv_common_pkg::MACHINE_EXTERNAL_INT : 'h0;

これで一応動くようになった。

209206 : 162798 : PC=[0000000080002096] (M,08,01) 0000e07e c.sdsp t6, 0(sp) MW8(0x0000000080022f80)=>0000000000000000 val1 = 8000000a00006000, val2 = 8000000a00006000 836830 : L1D Load-In : 80022f90(00249) : 00000000_80002c08_00000000_00000000 836830 : Load ISS Check : 80022f90 : 00000000_80002c08_00000000_00000000 836834 : L1D Stq Store : 80022f90(00249) : 00000000_80002c08_00000000_00000000 836834 : STQ ISS Check : 80022f90 : 00000000_80002c08_00000000_00000000 209212 : RTL(9,1) Exception Cause = CSR Update Flush(27) PC=000080002098, Inst=342025f3, csrr a1, mcause 209212 : 162799 : PC=[0000000080002098] (M,09,01) 342025f3 csrr a1, mcause val1 = 8000000000000007, val2 = 8000000000000007 GPR[11](4) <= 8000000000000007 836854 : L1D Load-In : 80022f80(00248) : 00000000_00000000_00000000_00000000 836854 : Load ISS Check : 80022f80 : 00000000_00000000_00000000_00000000 836858 : L1D Stq Store : 80022f80(00248) : 00000000_00000000_00000000_00000000 836858 : STQ ISS Check : 80022f80 : 00000000_00000000_00000000_00000000 209228 : RTL(0,1) Exception Cause = CSR Update Flush(27) PC=00008000209c, Inst=344027f3, csrr a5, mip 209228 : 162800 : PC=[000000008000209c] (M,00,01) 344027f3 csrr a5, mip val1 = 80, val2 = 80

次は、Returnだ。ここも何かがおかしい。

GPR[31](13) <= 0000000000000000 213540 : 163906 : PC=[0000000080002106] (M,01,02) 00006109 c.addi16sp sp, 128 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 80023000, val2 = 80023000 GPR[02](46) <= 0000000080023000 213546 : RTL(2,1) Exception Cause = MRET Flush(24) PC=000080002108, Inst=30200073, mret 213546 : 163907 : PC=[0000000080002108] (M,02,01) 30200073 mret 213575 : 163908 : PC=[0000000080002300] (M,09,01) e91ff06f j pc - 0x170 MR4(0x0000000080002f30)=>0000000000000000 ========================================== Wrong PC: RTL = 0000000080002300, ISS = 0000000080002b9a ========================================== =============================== SIMULATION FINISH : FAIL (CODE=100) ===============================