自作CPUに対して割込みコントローラの実装をしているが、久しぶりに時間ができたのでこれの修正を行っている。

割込みのかけ方だが、もう一度考え直すことにした。BOOMの実装方法を参考にしている。

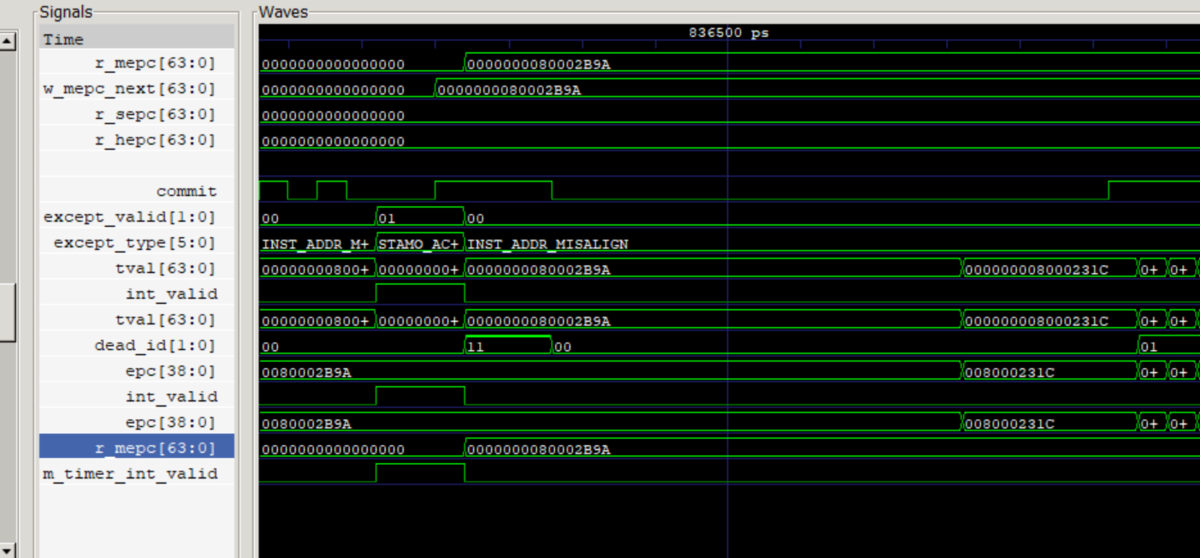

- 割込み要求信号がCSRから挿入されると、ROBの次にコミットされる命令がInterruptかつDead状態に変更される

- コミット時にこれを検出して、割込み先アドレスにフェッチを変更する。

このほうが処理がしやすいような気がしてきた。Spike側の処理は、これまではROB時にsim_int_insertedが挿入されたときにmtimeをアップデートする方法でSpike側に挿入している。

上記の方式でも、そのまま対応できるはずだ。早速実装してみると、結構簡単にうまくいった。

val1 = 0, val2 = 0 GPR[30](41) <= 0000000000000000 213542 : 163893 : PC=[0000000080002104] (M,14,01) 00006f82 c.ldsp t6, 0(sp) MR8(0x0000000080022f80)=>0000000000000000 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 0, val2 = 0 GPR[31](13) <= 0000000000000000 213542 : 163894 : PC=[0000000080002106] (M,14,02) 00006109 c.addi16sp sp, 128 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 80023000, val2 = 80023000 GPR[02](46) <= 0000000080023000 213548 : RTL(15,1) Exception Cause = MRET Flush(24) PC=000080002108, Inst=30200073, mret 213548 : 163895 : PC=[0000000080002108] (M,15,01) 30200073 mret 854274 : L1D Load-In : 80002f30(00243) : 00000011_00000010_00000000_00000001 854274 : Load ISS Check : 80002f30 : 00000011_00000010_00000000_00000001 854290 : L1D Evict : 80022f30(00243) : 00000000_800020c4_00000000_00000000 854290 : EVict ISS Check : 80022f30 : 00000000_800020c4_00000000_00000000 213576 : 163896 : PC=[0000000080002b9a] (M,04,01) 0000429c c.lw a5, 0(a3) MR4(0x0000000080002f30)=>0000000000000001