自作CPUに対して割込みコントローラの実装をしているが、久しぶりに時間ができたのでこれの修正を行っている。

結局割込み挿入の方針は以下に変えた。

- あるいは、割込み要求信号が一度フェッチモジュールでAcceptされると、それ以降は割込み挿入リクエストを取り下げてしまったほうがいいかもしれない。そっちのほうが楽そうな気がする。

こうしてフェッチモジュール内で割り込み要求信号をいったん受け入れてしまう。CSRモジュールは割込み要求信号はトリガーの形式で上げてしまう。 こうすると、MIE/MIPの存在価値がなくなってしまう気もするが、たぶん大丈夫。

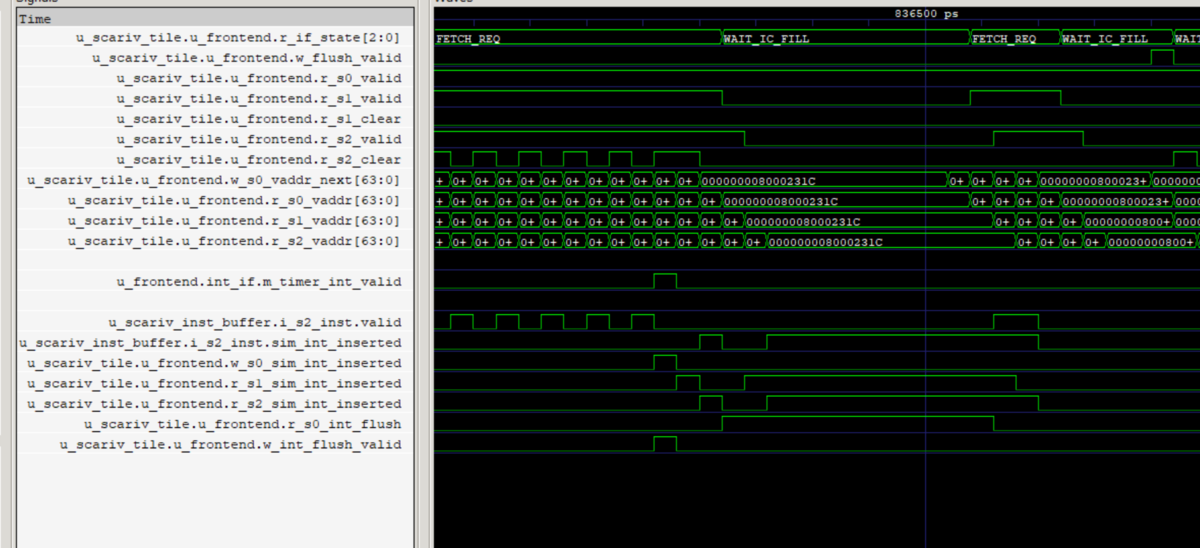

これにより、一応割込みがかかって、Spikeもそれに追従してくれた。

MR4(0x0000000080002f30)=>0000000000000000 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 0, val2 = 0 GPR[15](17) <= 0000000000000000 209127 : 162778 : PC=[0000000080002b9c] (M,03,02) fef77fe3 bgeu a4, a5, pc - 2 val1 = 8000000a00006000, val2 = 8000000a00006000 209129 : 162779 : PC=[0000000080002b9a] (M,04,01) 0000429c c.lw a5, 0(a3) MR4(0x0000000080002f30)=>0000000000000000 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 0, val2 = 0 GPR[15](18) <= 0000000000000000 209129 : 162780 : PC=[0000000080002b9c] (M,04,02) fef77fe3 bgeu a4, a5, pc - 2 val1 = 8000000a00006000, val2 = 8000000a00006000 /// ---------------------------------- /// ここで割り込みがかかった /// ---------------------------------- 209136 : 162780 : PC=[000000008000231c] (M,05,01) d5bff06f j pc - 0x2a6 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 0, val2 = 0 GPR[00](0) <= 0000000000000000 209167 : 162782 : PC=[0000000080002076] (M,09,01) 00007119 c.addi16sp sp, -128 val1 = 8000000a00006000, val2 = 8000000a00006000 val1 = 80022f80, val2 = 80022f80 GPR[02](1) <= 0000000080022f80 209167 : 162783 : PC=[0000000080002078] (M,09,02) 0000fc86 c.sdsp ra, 120(sp) MW8(0x0000000080022ff8)=>0000000080002b90

問題はそのあとだ。どうも差分が発生しているらしい。割込み要因レジスタだな。

MW8(0x0000000080022f88)=>0000000000000000 val1 = 8000000a00006000, val2 = 8000000a00006000 209206 : 162798 : PC=[0000000080002096] (M,08,01) 0000e07e c.sdsp t6, 0(sp) MW8(0x0000000080022f80)=>0000000000000000 val1 = 8000000a00006000, val2 = 8000000a00006000 836830 : L1D Load-In : 80022f90(00249) : 00000000_80002c08_00000000_00000000 836830 : Load ISS Check : 80022f90 : 00000000_80002c08_00000000_00000000 836834 : L1D Stq Store : 80022f90(00249) : 00000000_80002c08_00000000_00000000 836834 : STQ ISS Check : 80022f90 : 00000000_80002c08_00000000_00000000 209212 : RTL(9,1) Exception Cause = CSR Update Flush(27) PC=000080002098, Inst=342025f3, csrr a1, mcause 209212 : 162799 : PC=[0000000080002098] (M,09,01) 342025f3 csrr a1, mcause val1 = 8000000000000007, val2 = 8000000000000000 ========================================== Wrong GPR[11](4): RTL = 8000000000000000, ISS = 8000000000000007 ========================================== =============================== SIMULATION FINISH : FAIL (CODE=100) ===============================

修正していく。