前々から噂されていた、MIPSがRISC-Vを作っている話、正式発表があったようだ。

PシリーズとかIシリーズとかMIPSの時代からあった名前なので、それがそのまま踏襲されてしまっている。ただし中身はRISC-V。

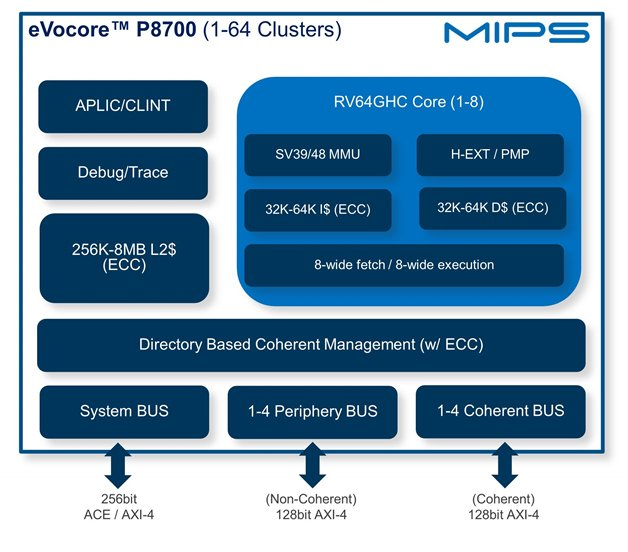

eVocore P8700

これはかつてのMIPS Pシリーズの継承でしょうね。

こちらの記事ではもうちょっと詳しいことが書いてある。

- Multi-issue superscalar Out of Order (OOO) with Multi-threading

- 16-stage pipeline for higher clock frequency

- 8-wide instruction fetch

- 8-execution pipes: 2xALU, MDU, 2xFPU, 2xMemory

- Enhanced Coherence Manager with L2 cache

- HW pre-fetch, widened busses, reduced latency

- 48-bit physical addressing

- 256 Interrupt support, APLIC/CLINT

- System interface

図を見る限りはRV64GHC、つまり、ハイパーバイザー対応ということになる。

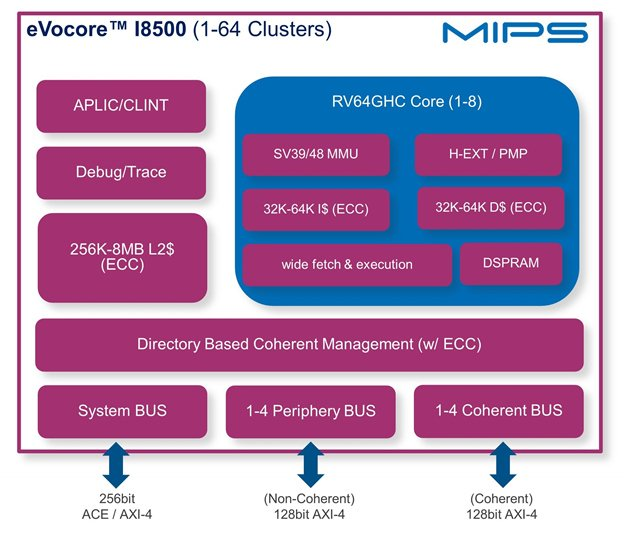

eVocore I8500

これはかつてのMIPS Iシリーズの継承でしょうね。

- インオーダパイプライン

- マルチスレッド対応

3命令発行パイプライン

In-Order with Simultaneous Multi-threading (SMT)

- 9-stage pipeline for efficient execution

- Wide instruction fetch

- 7-execution pipes: ALU, MDU, 2xFPU, 2xMemory

- Enhanced Coherence Manager with L2 cache

- HW pre-fetch, widened busses, reduced latency

- 48-bit physical addressing

- 256 Interrupt support, APLIC/CLINT

- System interface

こちらも図を見る限りはRV64GHC、ハイパーバイザー拡張だ。