Vivado-HLSを使って簡単なRISC-V CPUを作ってみている。

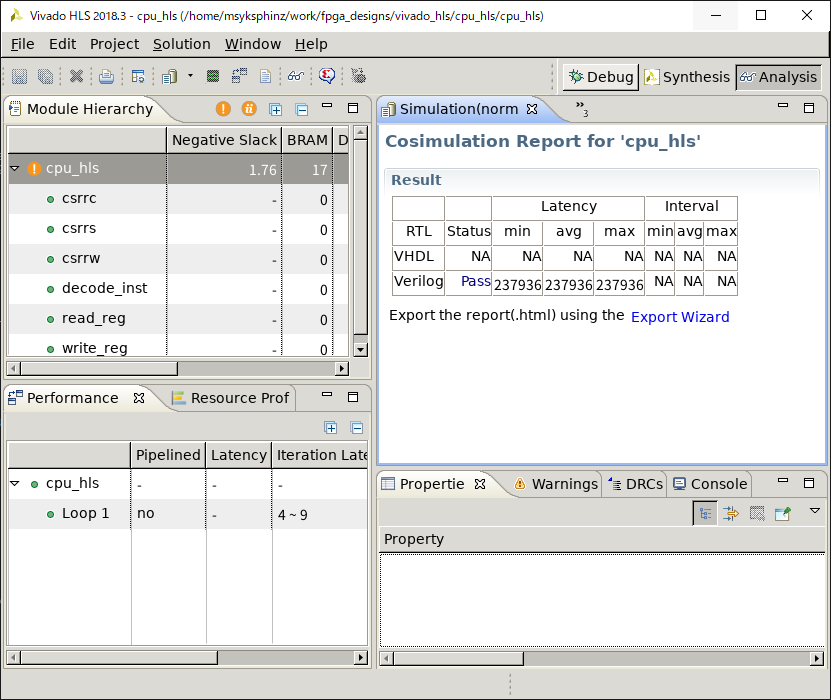

とりあえず基本的なパタンが動くようになったので、Co-Simulationの実施とサイクル測定を実施する。 Co-Simulationを実施すると、RTLシミュレーションでも無事に動作していることが確認できた。 では、サイクル数を測定する。

現在実行しているのはrv32ui-p-simpleという最も簡単なテストパタンだが、Vivado-HLSのレポートを見るとものすごいサイクル数がかかっている。 55命令程度の簡単なパタンだけれども、237936サイクルもかかっているって本当?

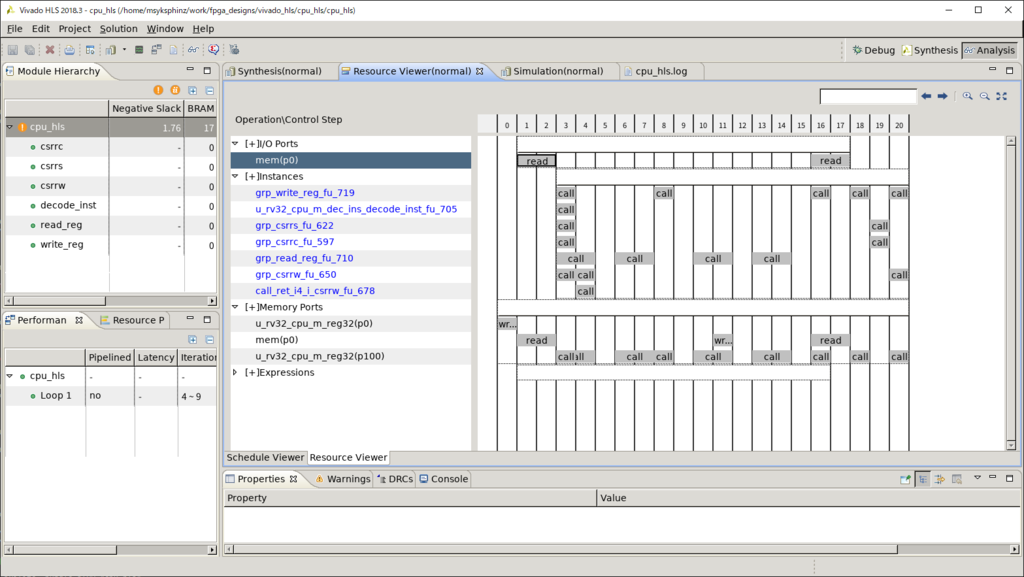

RTLの動作を確認するためにサイクル確認をしてみると、意外にサイクルを消費していないように見えるぞ? っていうか見方が分からん。

パイプライン化するとどうなるのだろう?ということで以下のディレクティブを挿入したのだが、論理合成に失敗してしまった。

diff --git a/vivado_hls/cpu_hls/cpu_hls.cpp b/vivado_hls/cpu_hls/cpu_hls.cpp index 128a5a1..0e73261 100644 --- a/vivado_hls/cpu_hls/cpu_hls.cpp +++ b/vivado_hls/cpu_hls/cpu_hls.cpp @@ -9,7 +9,7 @@ XLEN_t cpu_hls (uint32_t mem[MEMORY_SIZE]) { rv32_cpu u_rv32_cpu (mem, 0x1000, 0x1004); - do { + L0:do { u_rv32_cpu.fetch_inst(); u_rv32_cpu.decode_inst(); u_rv32_cpu.execute_inst(); diff --git a/vivado_hls/cpu_hls/directives.tcl b/vivado_hls/cpu_hls/directives.tcl index 980ab9b..2f64891 100644 --- a/vivado_hls/cpu_hls/directives.tcl +++ b/vivado_hls/cpu_hls/directives.tcl @@ -1,2 +1,4 @@ +set_directive_pipeline -II 2 "cpu_hls/L0" + set_directive_interface -mode s_axilite -bundle slv0 "cpu_hls" set_directive_interface -mode s_axilite -bundle slv0 "cpu_hls" mem