Vivado-HLSを使って簡単なRISC-V CPUを作ってみている。

s_axiliteとm_axiの違いで動作しなくなってしまい苦労していたが、色々調べていると、#pragmaでいろんなところにm_axiを入れていけば解決することが分かり、無事にデザインを合成することができた。

diff --git a/vivado_hls/cpu_hls/rv32_cpu.cpp b/vivado_hls/cpu_hls/rv32_cpu.cpp index ec7ca3e..3bbafc0 100644 --- a/vivado_hls/cpu_hls/rv32_cpu.cpp +++ b/vivado_hls/cpu_hls/rv32_cpu.cpp @@ -6,6 +6,7 @@ rv32_cpu::rv32_cpu(uint32_t *data_mem, Addr_t tohost_addr, Addr_t fromhost_addr) : m_data_mem(data_mem), m_tohost_addr(tohost_addr), m_fromhost_addr(fromhost_addr) { +#pragma HLS INTERFACE m_axi port=data_mem bundle=mem

diff --git a/vivado_hls/cpu_hls/cpu_hls.cpp b/vivado_hls/cpu_hls/cpu_hls.cpp index edeaf15..5f2e330 100644 --- a/vivado_hls/cpu_hls/cpu_hls.cpp +++ b/vivado_hls/cpu_hls/cpu_hls.cpp @@ -7,6 +7,7 @@ XLEN_t cpu_hls (uint32_t mem[MEMORY_SIZE]) { +#pragma HLS INTERFACE m_axi port=mem bundle=mem rv32_cpu u_rv32_cpu (mem, 0x1000, 0x1004); uint32_t test_counter = 0;

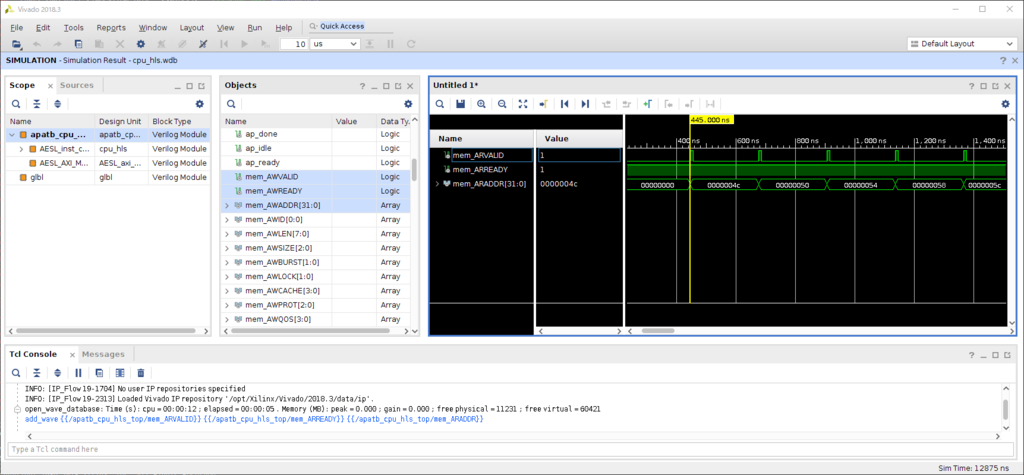

これで一応Cosimulationまで動作するようになった。ばんざい! サイクル数を確認すると1200サイクルくらいだ。前回よりはよっぽど改善している。 それでも、55命令を実行するのに1200サイクルは遅いなあ。

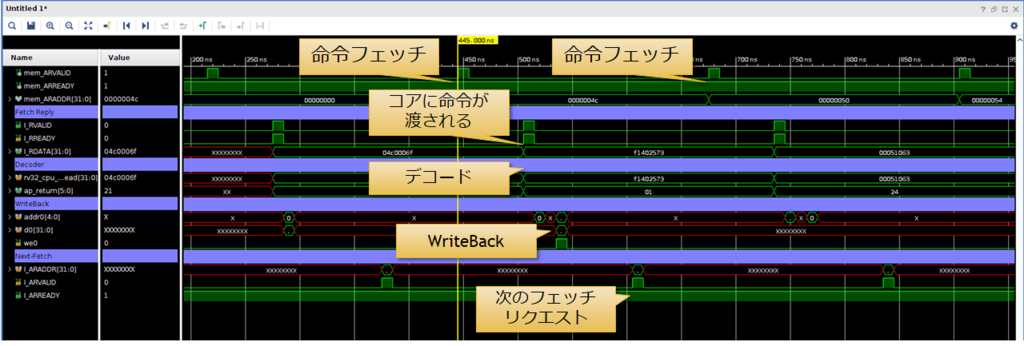

Cosimulationの際に、波形を取るようにしたので波形をダンプしてみた。

うーん、フェッチがかなりとびとびになっている。これは性能出ないわな。

大きいのは次のフェッチまでの時間が空きすぎていること。FIFOの中にフェッチリクエストが入っているままだけど、これはどのような仕組みになっているんだ?