自作RISC-Vアウトオブオーダコアがある程度安定し始めたので、久しぶりにVivadoの論理合成を流して様子を確認してみた。

その間に、いくつかVivadoでないと見つけられないエラーを直した。やっぱりVerilatorだけだとちょっと厳しいものがあるなあ。

とりあえずまずはタイミングレポートから。制約は書けていないが相当長いパスが出てしまっている。 これは気にしていた通りフロントエンドの命令発行に関する部分だ。命令を切り出してディスパッチ用の構造を作り込むところに問題がありそうだ。

Timing Report

Slack: inf

Source: u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_loop[2].r_inst_queue_reg[2][pc][1]/C

(rising edge-triggered cell FDCE)

Destination: u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/r_credits_reg[5]/D

Path Group: (none)

Path Type: Max at Slow Process Corner

Data Path Delay: 52.926ns (logic 11.293ns (21.337%) route 41.633ns (78.663%))

Logic Levels: 68 (CARRY4=3 FDCE=1 LUT2=1 LUT3=4 LUT4=10 LUT5=6 LUT6=38 MUXF7=4 MUXF8=1)

Location Delay type Incr(ns) Path(ns) Netlist Resource(s)

------------------------------------------------------------------- -------------------

FDCE 0.000 0.000 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_loop[2].r_inst_queue_reg[2][pc][1]/C

FDCE (Prop_fdce_C_Q) 0.478 0.478 f u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_loop[2].r_inst_queue_reg[2][pc][1]/Q

net (fo=2, unplaced) 0.976 1.454 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/inst_buf_loop[2].r_inst_queue_reg[2][pc]__0__0[0]

LUT6 (Prop_lut6_I0_O) 0.295 1.749 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_head_start_pos[1]_i_4/O

net (fo=103, unplaced) 1.002 2.751 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_head_start_pos[1]_i_4_n_0

LUT6 (Prop_lut6_I0_O) 0.124 2.875 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/sc_disp\\.tlb_except_cause[0][0]_i_6/O

net (fo=17, unplaced) 0.505 3.380 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/sc_disp\\.tlb_except_cause[0][0]_i_6_n_0

LUT6 (Prop_lut6_I4_O) 0.124 3.504 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][inst][14]_i_49/O

net (fo=256, unplaced) 0.572 4.076 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][inst][14]_i_49_n_0

LUT4 (Prop_lut4_I2_O) 0.124 4.200 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][inst][1]_i_47/O

net (fo=1, unplaced) 0.902 5.102 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][inst][1]_i_47_n_0

LUT6 (Prop_lut6_I3_O) 0.124 5.226 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][inst][1]_i_17/O

net (fo=1, unplaced) 0.000 5.226 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][inst][1]_i_17_n_0

MUXF7 (Prop_muxf7_I1_O) 0.247 5.473 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst_reg[0][inst][1]_i_9/O

net (fo=2, unplaced) 0.000 5.473 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst_reg[0][inst][1]_i_9_n_0

MUXF8 (Prop_muxf8_I0_O) 0.098 5.571 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst_reg[0][rvc_inst_valid]_i_3/O

net (fo=1, unplaced) 0.717 6.288 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst_reg[0][rvc_inst_valid]_i_3_n_0

LUT5 (Prop_lut5_I0_O) 0.319 6.607 f u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_disp_inst[0][rvc_inst_valid]_i_2/O

...

LUT6 (Prop_lut6_I1_O) 0.124 47.533 f u_msrh_tile/u_msrh_resource_alloc/u_csu_credit_return/r_head_ptr[4]_i_9__0/O

net (fo=2, unplaced) 0.460 47.993 u_msrh_tile/u_msrh_fp_rename/free_loop[4].u_freelist/w_resource_ok

LUT6 (Prop_lut6_I3_O) 0.124 48.117 r u_msrh_tile/u_msrh_fp_rename/free_loop[4].u_freelist/r_head_ptr[4]_i_3__4/O

net (fo=9, unplaced) 0.490 48.607 u_msrh_tile/u_rob/u_cmt_ptr/r_head_start_pos_reg[0]_0

LUT3 (Prop_lut3_I2_O) 0.124 48.731 f u_msrh_tile/u_rob/u_cmt_ptr/r_disp_inst[1][brtag][0]_i_3/O

net (fo=10, unplaced) 0.492 49.223 u_msrh_tile/u_frontend/u_ftq/u_ptr/w_iq_disp\\.ready

LUT6 (Prop_lut6_I4_O) 0.124 49.347 r u_msrh_tile/u_frontend/u_ftq/u_ptr/r_disp_inst[2][brtag][2]_i_2/O

net (fo=71, unplaced) 0.540 49.887 u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/r_credits_reg[0]_3

LUT3 (Prop_lut3_I1_O) 0.124 50.011 r u_msrh_tile/u_frontend/u_msrh_inst_buffer/inst_buf_ptr/w_credits_next0_carry_i_3__0/O

net (fo=1, unplaced) 0.639 50.650 u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry_i_6_0[0]

CARRY4 (Prop_carry4_DI[1]_O[3])

0.629 51.279 r u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next0_carry/O[3]

net (fo=1, unplaced) 0.618 51.897 u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next0_carry_n_4

LUT3 (Prop_lut3_I2_O) 0.307 52.204 r u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry_i_3/O

net (fo=1, unplaced) 0.000 52.204 u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry_i_3_n_0

CARRY4 (Prop_carry4_S[3]_CO[3])

0.376 52.580 r u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry/CO[3]

net (fo=1, unplaced) 0.009 52.589 u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry_n_0

CARRY4 (Prop_carry4_CI_O[1])

0.337 52.926 r u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry__0/O[1]

net (fo=1, unplaced) 0.000 52.926 u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/w_credits_next_carry__0_n_6

FDPE r u_msrh_tile/u_msrh_resource_alloc/alu_cre_ret_loop[0].u_alu_credit_return/r_credits_reg[5]/D

------------------------------------------------------------------- -------------------

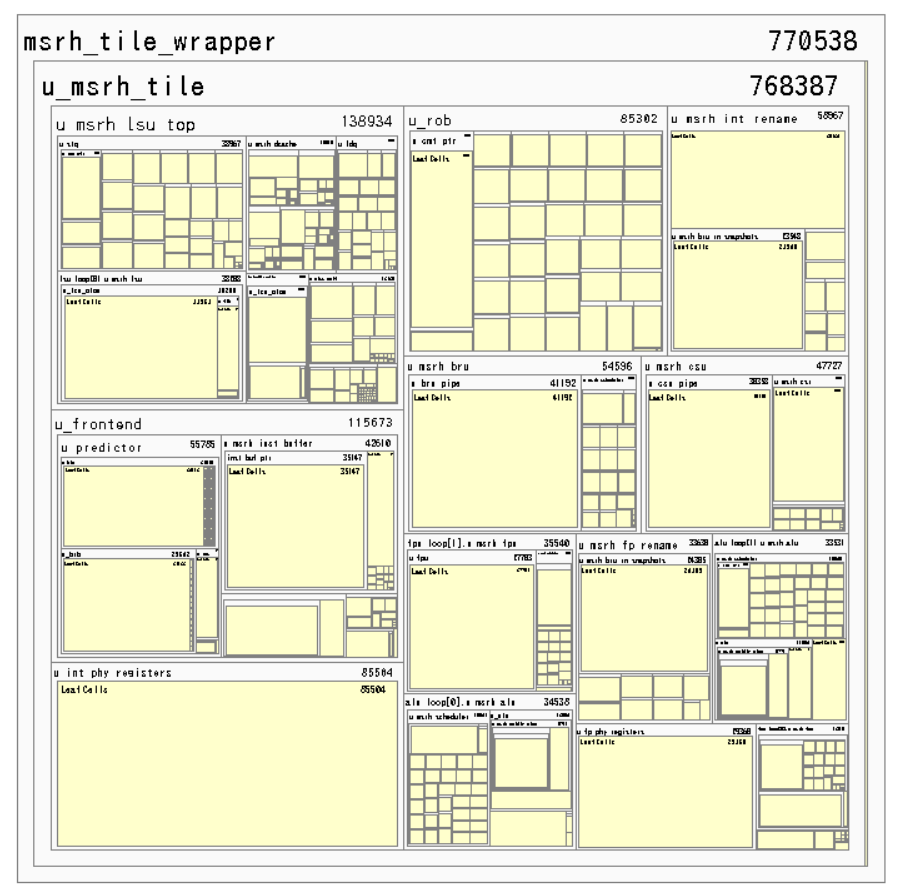

何となく合成後の様子。インスタンスの雰囲気としては問題なさそう。