分岐予測は設計経験がないうえにいろいろ試行錯誤しながら作っているのだが、なかなか性能が伸びない。

時間を見つけて実装の見直しを行っているが、独自にいろいろやってもらちが明かないので論文を読んでみることにした。 参考にしたのは以下の論文「Improving Prediction for Procedure Returns with Return-Address-Stack Repair Mechanism」というもの。

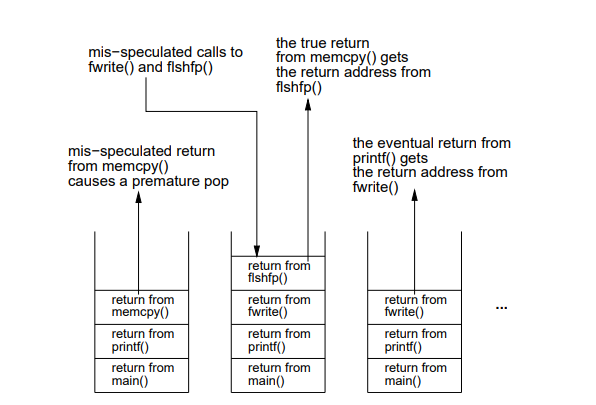

内容としては私の疑問点にかなりマッチしている。要するにCALLとRETが投機実行されてRASのインデックスが過剰に更新されてしまった場合にどうするかという話。 そこまでの経緯が図を使って詳細に説明されている。これは自分も全く同じ境遇になっているので良くわかる。

で、問題の解決方法だが、割とシンプルに「ロールバックすればよい」とだけ書いてあってそれをどうハードウェアで実現するのかを知りたかったのに、あまりそこには触れられていなかった。 途中からは性能評価の話になってしまったので途中から読むのをやめている。

やはりCALL命令を過剰にフェッチした場合にはその分だけロールバックさせなければならないということか。もう少しこれまでの実装を確認して実装方法を変更しよう。