ISCAの上記の論文を読む。現在は入手不可能になっているが、ISCAの時は特別に公開されていたようだ。あんまり詳細は記述できないのだがサマリだけをメモ的にアップロードしていく。

最新のエンタープライズクラスのIBM z15分岐予測器の設計について説明する。

- IBM z15の分岐予測器の主要な動作と機能

- パイプライン

- 予測のための構造

- 検証方法

を紹介する。

1. イントロダクション

IBM z15はメインフレーム向けのプロセッサである。これらのシステムはあらゆるワークロードに対して高性能に実行可能なように設計されており、通常はデータベース処理に対して最適化されている。

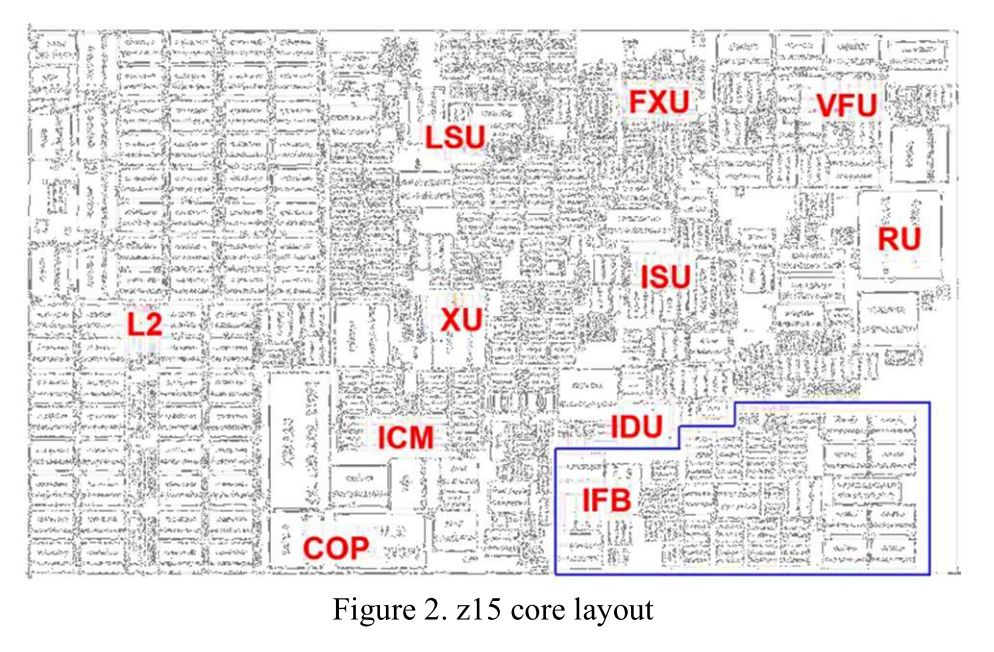

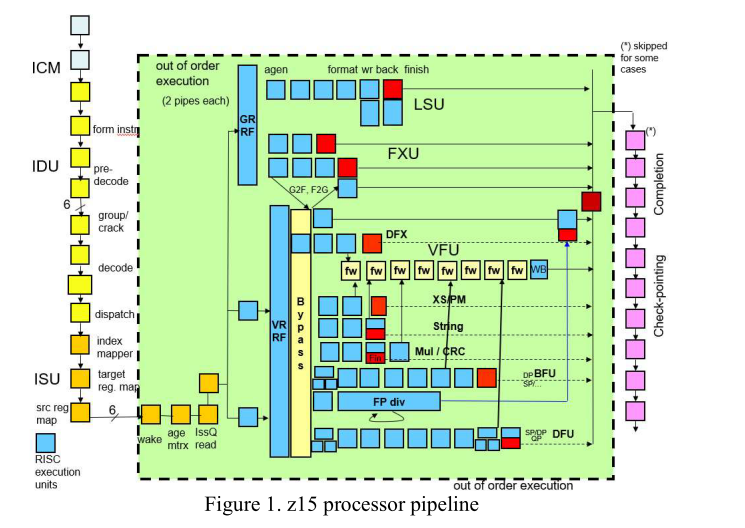

IBM z15はスーパスカラ、SMT(Simultaneous Multi Threading)、アウトオブオーダコアであり、5.2GHzで動作する。図1.に示すような深いパイプラインを持っており、6命令まで同時発行できるプロセッサである。このプロセッサは非常にパイプラインが深いため、分岐予測の精度が非常に重要となる。z15は4階層のキャッシュ改装を採用しており、240個のプロセッサコアのうち190個を使用可能となっている。CP(Central Processor)は12個のCPUコアを含んでおり、1つのL3キャッシュを共有している。4つのCPチップはSC(System Control)チップと通信することができる。このプロセッサはz/アーキテクチャ[3]に準拠している。z/アーキテクチャは分岐命令としてインダイレクト分岐と相対分岐に分類されている。

| zEC12 (32nm) | z13 (22nm) | z14 (14nm) | z15 (14nm) | |

|---|---|---|---|---|

| CPチップ | 6コア | 8コア | 10コア | 12コア |

| オンチップキャッシュサイズ | L1I : 64K, L1D: 96K L1+ : 1MB Private L2 : 1MB Private L3 : 48MB Shared |

L1I : 96K, L1D : 128K L2I : 2MB Private L2D : 2MB Private L3 : 63MB Shared |

L1I : 128K, L1D : 128K L2I : 2MB Private L2D : 4MB L3 : 128MB Shared |

L1I : 128K, L1D : 128K L2I : 4MB Private L2D : 4MB L3 : 256MB Shared |

| 分岐予測 | BTB1 : 4K (1k x 4way) BTB2 : 24K (6way) PHT : 4K CTB : 2K |

BTB1 : 6K (1K x 6way) BTB2 : 96K (6way) PHT : 6K CTB : 2K |

BTB1 : 8K (2K x 4way) BTB2 : 128K (4way) PHT : 8K CTB : 2K |

BTB1 : 16 (2K x 8way) BTB2 : 128K (6way) PHT : 8K CTB : 2K |

分岐予測は、命令フェッチ・分岐予測ユニット (IFB)によって担当される。分岐命令がデコードされると、動的に予測された分岐の情報はIDUによる命令よりも優先的に使用されて、次の命令のフェッチに使用される。