RISC-VのオープンソースプロセッサBOOMv3(SonicBOOM)が公開されているが、シミュレーションを行うためにはChipyardの環境を用意するのが原則になっているようだ。

Chipyardの環境はかなり巨大なので用意するのが面倒なのだが、構築方法を忘れそうなので一応メモしておく。

基本的には以下のチュートリアルに則る。環境はWSLのUbuntu 18.04だ。

リビジョンはTAG 1.3.0を使用している。

git clone https://github.com/ucb-bar/chipyard.git

cd chipyard

./scripts/init-submodules-no-riscv-tools.sh

riscv-toolsはChipyardのものを使っておくのが安心な気がする。

MAKEFLAGS="-j$(nproc) ./scripts/build-toolchains.sh riscv-tools

BOOMv3のビルドにはMediumBoomConfigを使用する。MegaBoomConfigを試行したがメモリが足りなさ過ぎて動作しなかった。っていうか無理やりヒープ領域を増やしたらWindowsごと落ちてしまった。

diff --git a/variables.mk b/variables.mk index 4d49d5f..0e8c983 100644 --- a/variables.mk +++ b/variables.mk @@ -117,7 +117,7 @@ sim_common_files ?= $(build_dir)/sim_files.common.f ######################################################################################### # java arguments used in sbt ######################################################################################### -JAVA_HEAP_SIZE ?= 8G +JAVA_HEAP_SIZE ?= 100G JAVA_ARGS ?= -Xmx$(JAVA_HEAP_SIZE) -Xss8M -XX:MaxPermSize=256M #########################################################################################

cd sims/verilator/ make CONFIG=MediumBoomConfig

シミュレーションの実行にはrun-bmark-testsを使用する。これでベンチマーク一式が測れる。

make CONFIG=MediumBoomConfig run-bmark-tests

[ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/median.riscv.out Completed after 30841 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/multiply.riscv.out Completed after 53063 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/qsort.riscv.out Completed after 329075 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/towers.riscv.out Completed after 19261 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/vvadd.riscv.out Completed after 20004 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/dhrystone.riscv.out Completed after 151856 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/mt-matmul.riscv.out Completed after 34710 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/mm.riscv.out Completed after 276499 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/spmv.riscv.out Completed after 137791 cycles [ PASSED ] /home/msyksphinz/work/riscv/chipyard/chipyard/sims/verilator/output/chipyard.TestHarness.MediumBoomConfig/mt-vvadd.riscv.out Completed after 104985 cycles

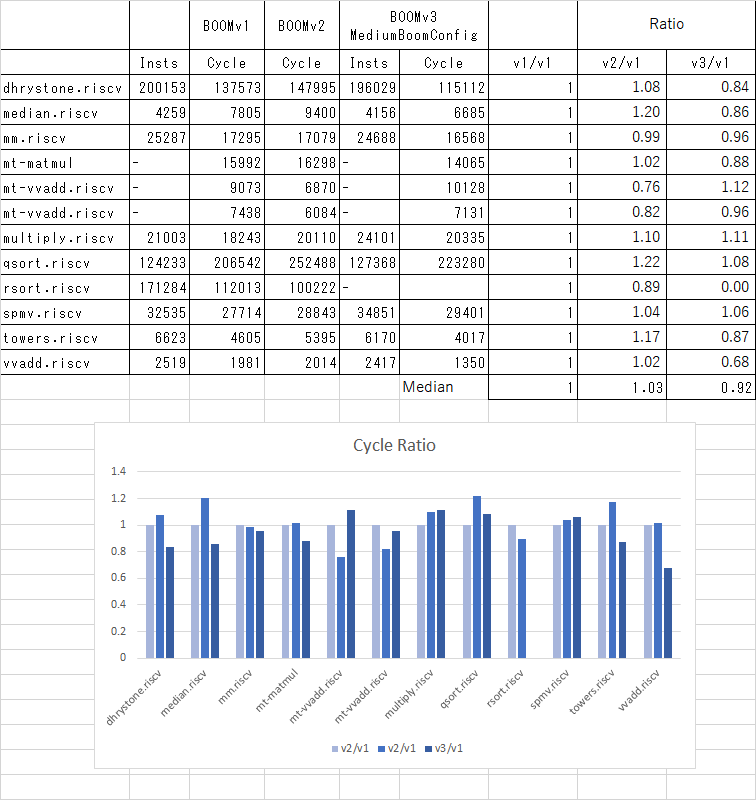

ログをベースにしてこれまでの測定結果からベンチマークのサイクル結果を比較しなおしてみた。

| BOOMv1 | BOOMv2 | BOOMv3(MediumBoomConfig) | |||

|---|---|---|---|---|---|

| Insts | Cycle | Cycle | Insts | Cycle | |

| dhrystone.riscv | 200153 | 137573 | 147995 | 196029 | 115112 |

| median.riscv | 4259 | 7805 | 9400 | 4156 | 6685 |

| mm.riscv | 25287 | 17295 | 17079 | 24688 | 16568 |

| mt-matmul | - | 15992 | 16298 | - | 14065 |

| mt-vvadd.riscv | - | 9073 | 6870 | - | 10128 |

| mt-vvadd.riscv | - | 7438 | 6084 | - | 7131 |

| multiply.riscv | 21003 | 18243 | 20110 | 24101 | 20335 |

| qsort.riscv | 124233 | 206542 | 252488 | 127368 | 223280 |

| rsort.riscv | 171284 | 112013 | 100222 | - | |

| spmv.riscv | 32535 | 27714 | 28843 | 34851 | 29401 |

| towers.riscv | 6623 | 4605 | 5395 | 6170 | 4017 |

| vvadd.riscv | 2519 | 1981 | 2014 | 2417 | 1350 |

だいたい10%程度のサイクル性能向上かな。