だいぶ遅れてしまっていたのだが、RISC-VのオープンソースプロセッサSweRV-EH2が公開されているので少し触ってみることにした。

SweRV-EH2のSoC構成状況は以下のようになっている。

コアはフロントエンド側を4ステージ、バックエンド側は5ステージで5パイプが用意されている。 Load/Storeパイプライン、整数パイプライン0、整数パイプライン1、乗算パイプライン、除算パイプランで構成されている。

とりあえずはビルド方法を確認する。

perlのモジュールが必要なので以下をインストールしておく。

sudo cpan install JSON

リポジトリの先頭で以下の環境偏すうRV_ROOTを設定しておく。

export RV_ROOT=${PWD}

以下でマルチスレッド版のコアをビルドする。テストベンチはcmark_mtでマルチスレッド用のCoremarkを実行するようになっている。

make -f $RV_ROOT/tools/Makefile target=default_mt TEST=cmark_mt

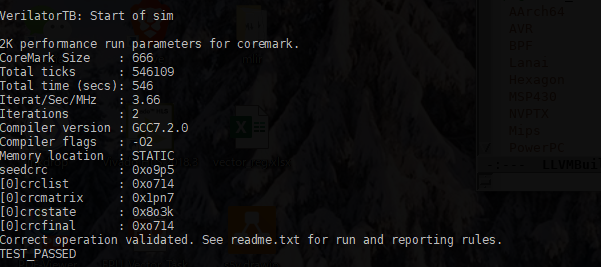

実行結果は以下のようになった。マルチスレッド版のCoremarkで3.66CMK/MHzだった。なかなか良いのではないか。

VerilatorTB: Start of sim 2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 546109 Total time (secs): 546 Iterat/Sec/MHz : 3.66 Iterations : 2 Compiler version : GCC7.2.0 Compiler flags : -O2 Memory location : STATIC seedcrc : 0xo9p5 [0]crclist : 0xo714 [0]crcmatrix : 0x1pn7 [0]crcstate : 0x8o3k [0]crcfinal : 0xo714 Correct operation validated. See readme.txt for run and reporting rules. TEST_PASSED

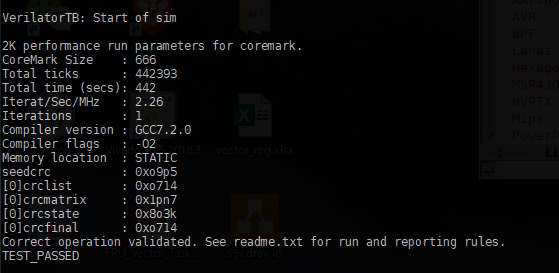

シングルスレッド版は以下のようになった。2.26CMK/MHzである。

VerilatorTB: Start of sim 2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 442393 Total time (secs): 442 Iterat/Sec/MHz : 2.26 Iterations : 1 Compiler version : GCC7.2.0 Compiler flags : -O2 Memory location : STATIC seedcrc : 0xo9p5 [0]crclist : 0xo714 [0]crcmatrix : 0x1pn7 [0]crcstate : 0x8o3k [0]crcfinal : 0xo714 Correct operation validated. See readme.txt for run and reporting rules.