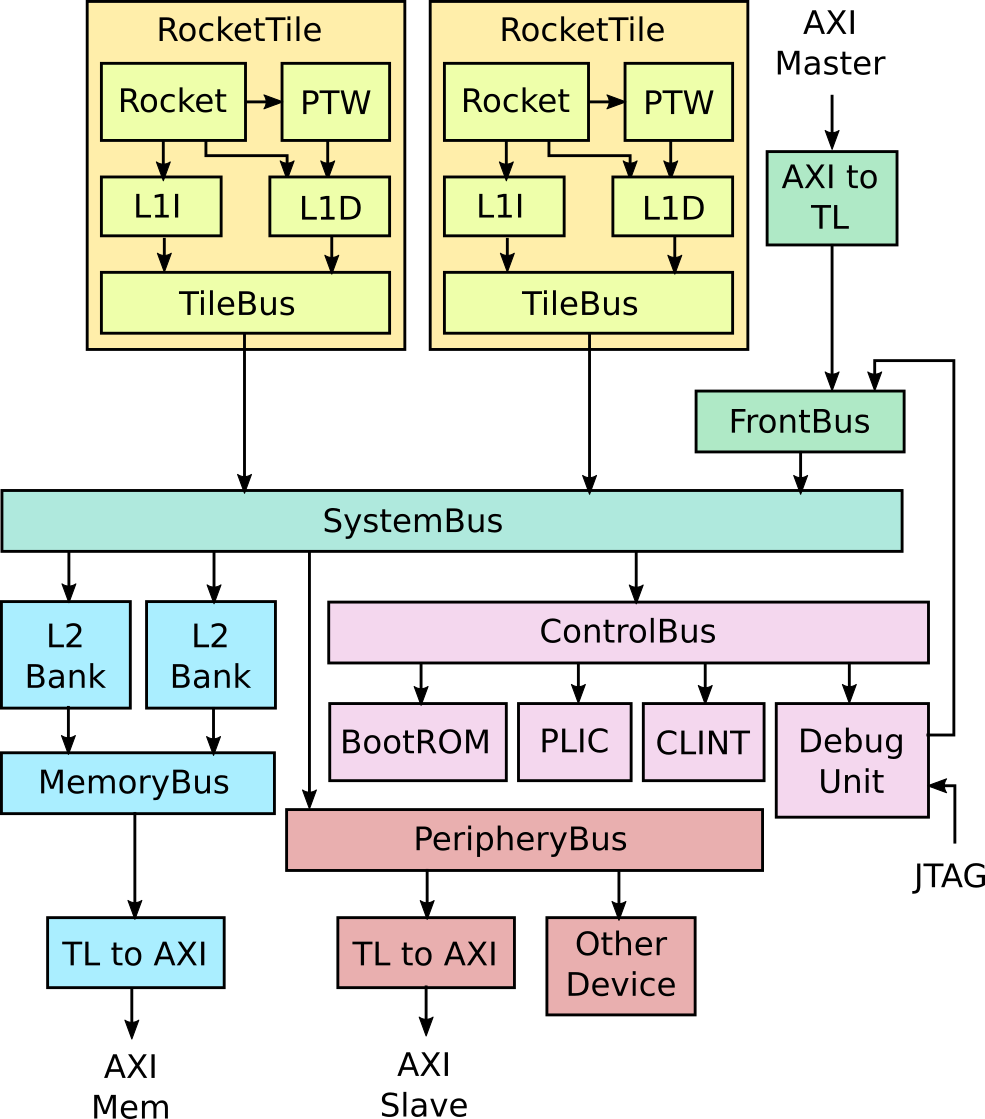

Chipyardに含まれるデザインには、InclusiveCacheと呼ばれるL2キャッシュに相当するもの?が含まれていた。 これまでにRocket-ChipにはL2に相当するものは含まれていなかったので面白そうだ。 まずはデザインを生成してみよう。

Configを調べていると、通常のRocket-Chipでも生成できそうだし、DualCoreConfigやMediumBoomConfigでも生成できそうである。

generators/example/src/main/scala/RocketConfigs.scala

class RocketConfig extends Config( new WithTop ++ // use default top new WithBootROM ++ // use default bootrom new freechips.rocketchip.subsystem.WithInclusiveCache ++ // use Sifive L2 cache new freechips.rocketchip.subsystem.WithNBigCores(1) ++ // single rocket-core new freechips.rocketchip.system.BaseConfig) // "base" rocketchip system class DualCoreRocketConfig extends Config( new WithTop ++ new WithBootROM ++ new freechips.rocketchip.subsystem.WithInclusiveCache ++ new freechips.rocketchip.subsystem.WithNBigCores(2) ++ // dual-core (2 RocketTiles) new freechips.rocketchip.system.BaseConfig)

generators/example/src/main/scala/BoomConfigs.scala

class MediumBoomConfig extends Config( new WithTop ++ new WithBootROM ++ new freechips.rocketchip.subsystem.WithInclusiveCache ++ new boom.common.WithMediumBooms ++ // 2-wide BOOM new boom.common.WithNBoomCores(1) ++ new freechips.rocketchip.system.BaseConfig)

生成するには、verilatorのディレクトリに言ってMakeコマンドをたたく。

cd sims/verilator make -j8 CONFIG=RocketConfig make -j8 CONFIG=DualCoreRocketConfig make -j8 CONFIG=MediumBoomConfig

生成されたVerilogを確認すると、InclusiveCacheを確認することができた。実際のScalaのコードは以下に実装してある。

generators/sifive-cache/craft/inclusivecache/src/InclusiveCache.scala

val scheduler = Module(new Scheduler(params))

generators/sifive-cache/craft/inclusivecache/src/Scheduler.scala

class Scheduler(params: InclusiveCacheParameters) extends Module { ... val bankedStore = Module(new BankedStore(params))

generators/sifive-cache/craft/inclusivecache/src/BankedStore.scala

class BankedStore(params: InclusiveCacheParameters) extends Module { ... val cc_banks = Seq.tabulate(numBanks) { i => DescribedSRAM( name = s"cc_banks_$i", desc = "Banked Store", size = rowEntries, data = UInt(width = codeBits) ) } ...

これが実際のRAMに相当するところだ。