NVDLAの内部構造についてもう少し詳しく解析したいのだが、割としっかりと解説してあるページがあったので読み進めていこう。

参考ににしたのは以下。っていうかNVDLA本家のページである。 今回はConvolutionのためのモジュール。Convolution DMA(CDMA)である。

- Unit Description (NVDLA)

Unit Description — NVDLA Documentation

畳み込みDMA

概要

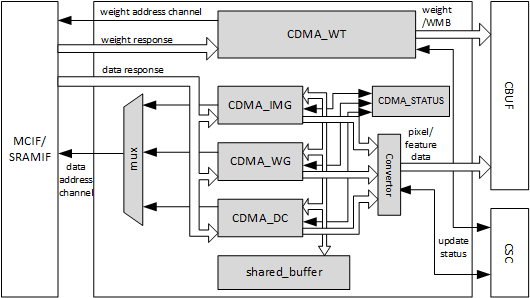

畳み込みDMA(CDMA)は畳み込みパイプラインを実行するパイプラインステージである。SRAM/DRAMからデータをフェッチしデータを畳み込みエンジンの処理できるようにバッファ(Convolution Buffer: CBUF)に格納する。サポートしている入力フォーマットは:

- ピクセルデータ

- 特徴データ

- 圧縮・非圧縮の重みデータ

- WMB

- WGS

CDMAからAXIに2つのチャネルが接続されている。重みデータの読み込みチャネルと、データ読み込みのためのチャネルである。上記の入力フォーマットをフェッチするために、チャネルは上記のフォーマットのために構成してある。以下の表には、読み込みチャネルにマッピングするための入力データフォーマットを示してある。

| 入力フォーマット | Image Case | Uncompressed Feature Case | Uncompressed Weight Case | Compressed Weight Case |

|---|---|---|---|---|

| Pixel data | data channel | NA | NA | NA |

| Uncompressed feature data | NA | data channel | NA | NA |

| Uncompressed weight | NA | NA | weight channel | NA |

| Sparse compressed weight | NA | NA | NA | weight channel |

| WMB | NA | NA | NA | weight channel |

| WGS | NA | NA | NA | weight channel |

畳み込みDMAはメモリの読み込みリクエストしか発行しない。すべてのメモリリクエストは64-byteのアドレスにアラインされて発行される。

CDMAは3つのサブモジュールから構成されており、ピクセルデータと特徴データをフェッチする: CDMA_DC, CDMA_WG, CDMA_IMGである。これらのサブモジュールの役割は似通っているが、データをCBUF RAMへ書き込むか順番が異なる。 どのような場合にも、サブモジュールのうちの1つがピクセル・特徴データをフェッチするためにアクティベートされる。

ここでは、CDMA_DCを例として取り上げる:

- Convolution Bufferの空き領域をチェックする。

- 読み込みトランザクションを生成する。

- フェッチデータを共有バッファにキャッシュする。

- 特徴キューブを正しい順番に整形する。

- Convolution Bufferの書き込みアドレスを生成する。

- CDMA_STATUSサブモジュール内のConvolution Bufferの状態をアップデートする。

Convolution DMAはWinogradの処理を実行するために所望のエンジンを使用する。CDMA_WGはCDMA_DCと非常に似通った構造をしているが、Convolution Buffer内の最終的な特徴データの構造は異なっている。したがってCDMA_WGは特殊なフェッチシーケンスを持っている。さらに、CDMA_WGはWinogradチャネル拡張を事項している。

CDMA_IMGエンジンはピクセルデータを外部メモリからフェッチする。データフォーマットに応じてアドレスを生成し、ピクセルの要素の順番を変更してConvolution Bufferの適切なエントリに書き込む。CDMA_IMGの動作はCDMA_DCに似ているが、ピクセルデータを扱うというところが異なる。

CDMA_DCエンジンのみがマルチバッチモードをサポートしている。したがって、1つ以上の入力特徴データキューブを1つのHWレイヤでフェッチすることができ、性能を向上させることができる。最大バッチサイズは32である。

CDMAは重みのフェッチにも所望のエンジンを使用する: CDMA_WTである。CDMA_WTは他のDMAエンジンと比較するとシンプルであるが、同時に3つのRead steamをサポートしているところが異なる。もし入力重みフォーマットが圧縮されていないと、重みデータのみをフェッチする。もし重みフォーマットが圧縮されていると、WMBとWSGはすべてフェッチされる。重みフォーマットについては、Data Formats の項目を参照すること。

入力重みデータが圧縮されていると、2つのアービタが有効差化されてRead streamが読み込まれる。最初の重みラウンドロビンアービタが重みストリームもしくはWMBストリームのリクエストを受け付ける。次にそのアービトレーションの勝者がWGSの読み込みストリームと静的なアービトレーションを行う。WGSは常に高い優先度を持っている。最終的に勝利したリクエストが重みチャネルにデータフェッチリクエストを発行する。

CDMA_WTは可能な限り重みのフェッチが完了するか、Convolution Bufferのエントリが空いている限りConvolution Bufferを埋めようとする。

CDMAはCBUF中の重みバッファと入力データバッファの通信状態を管理している。CDMAとCSCには2つの状態コピーが存在している。データ要素が解放されたときに、2つのモジュールがアップデートとリリース情報を交換し、新しい特徴データ・ピクセルデータ・重みデータをいつフェッチするのかを決めている。

電力について

Convolution DMAはデータパス上にクロックゲーティングが実施されている。Convolution DMAのデータパスのクロックは、データが存在しないか、プログラムレジスタにおいてハードウェアレイヤが構成されていないときにゲーティングさえっる。CDMAのレジスタファイルのサブモジュールはクロックゲーティングされないため、新しいコマンドは常に受け付けることができる。

Convolution Buffer

概要

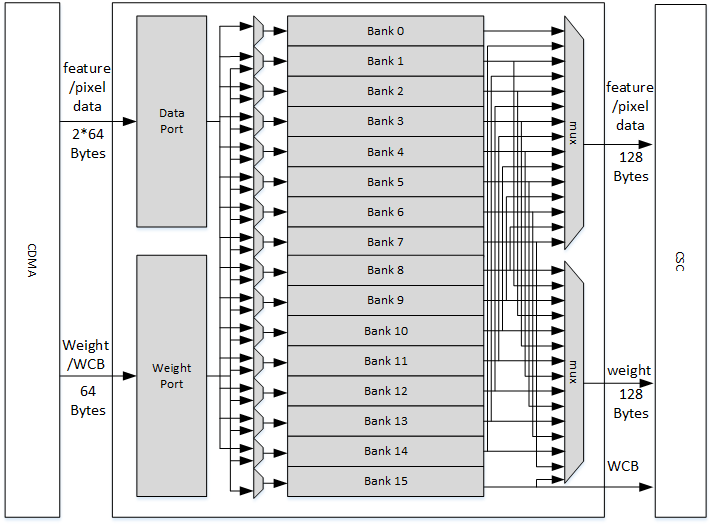

Convolution Buffer(CBUF)は畳み込みパイプライン中のステージである。512KBのSRAMで構成される。SRAMはCDMAモジュールからの入力ピクセルデータ・特徴データ・重みデータとWMBデータを読み取る。これにはConvolution Sequence Generatorモジュールを使用する。CBUFは2つの書き込みポートと3つの読み込みポートを持っている。

CBUFは32KBのメモリが16バンク用意されている。各バンクは512-bit幅であり、256エントリの2ポートのSRAMで構成されている。これらのバンクは3つの論理Circularバッファとして動作する。

- Input data buffer

- Weight buffer

- WMB buffer

- 入力データバッファ

- 重みバッファ

- WMBバッファ

重みフォーマットが圧縮されているとき、バンク15はWMBバッファとして割り当てられ、残りの2種類のバッファはバンク0~バンク14に格納される。重みフォーマットが圧縮されていないとき、WMBバッファはどのバンクにも割り当てられず、データバッファと重みバッファは16バンクのすべてを使用する。必要なバンク数が16よりも小さい場合は、残ったバンクは使用されない。

各バッファはCircularバッファとして使用される。新しい入力データ・重み・WMBはエントリアドレスを持っており、常に上位方向に加算される。もしアドレスが最大値に到達すると、0にラッピングされて0から再度インクリメントされる。

電力について

Convolution Bufferにはデータバス中のレジスタに対してクロックゲーティングが適用されている。Convolution Bufferのデータパスは、アイドル状態の場合か、プログラマブルレジスタによりどのHWレイヤも割り当てられていないとき、SLCGによりクロックゲーティングされる。Convolution Buffer内のコンフィグレーションレジスタはクロックゲーティングされず、したがって常にレジスタをプログラムすることができる。

畳み込みシーケンスコントローラ

概要

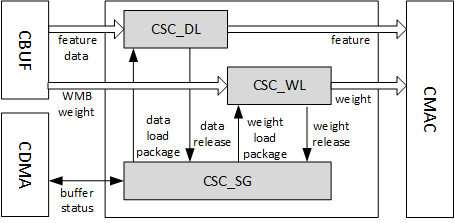

畳み込みシーケンスコントローラ(CSC)は入力特徴データ、ピクセルデータ、重みデータをCBUFからConvolution MACユニットに転送する役割を持つ。畳み込みパイプライン部において、畳み込みシーケンスの計算及び制御を行うためのカギとなるモジュールである。

畳み込みシーケンスコントローラ(CSC)3つのサブモジュールから構成されている: CSC_SG, CSC_WL, CSC_DLである。図55を参照のこと。

CSC_SGは畳み込みシーケンスジェネレータである。このモジュールは畳み込み操作の制御シーケンスを生成する。

CSC_SGのフローは以下の通りである。

- CBUF中に十分なデータと重みが格納されるまでポーリングする。

- シーケンスパッケージを生成する。シーケンスパッケージには、重みパッケージをロードするシーケンスと、データをロードするシーケンスが含まれる。各パッケージは1つのストライプ操作として表現される。

- 2つのパッケージをFIFOに挿入する。

- 重みと特徴・ピクセルのための2つのカウンタである。ダウンカウンタである。

- カウンタが0になると、Convolution Accumulatorからの信号をチェックしてバックプレッシャをチェックする。

- 全ての状態がReadyであれば、適切な時間に重みとデータパッケージをCSC_WLとCSC_DLに転送する。

CSC_DLは畳み込みデータローダである。このモジュールは特徴・ピクセルローディングのシーケンスを実行する論理が入っている。このモジュールはシーケンスジェネレータからパッケージを受け取り、特徴・ピクセルデータをCBUFからロードしてConvolution MACに転送する。データバッファの状態を管理し、CDMAとやり取り行って状態を常に最新に保つ。Winogradモードのために、入力特徴データを変換するためにPRA(Pre-addition)も行う役割がある。

CSC_WLはConvolution Weight Loaderの略である。このモジュールは重みをロードするシーケンサの論理が入っている。シーケンスジェネレータからパッケージを受け取り、CBUFから重み情報を受け取り、必要な回答処理を行ってからConvolution MACに転送する。重みバッファの状態を管理し、CDMA_WTと通信を行って状態を最新に保つ。

電力について

畳み込みシーケンスコントローラはデータパス中のレジスタに対してクロックゲーティングが適用される。畳み込みシーケンスコントローラのデータパス中のクロックは、アイドル中であるかプログラマブルレジスタによって有効化されていない場合、クロックゲーティングが適用される。畳み込みシーケンスコントローラのサブモジュールのレジスタファイルはクロックゲートされないため、常に最新の情報を入力できる。