ISCA 2020で発表されたAlibabaのXuantie-910の論文を読む。

- Xuantie-910: A Commercial Multi-Core 12-Stage Pipeline Out-of-Order 64-bit High Performance RISC-V Processor with Vector Extension

https://www.iscaconf.org/isca2020/papers/466100a052.pdf

概要

Xuantie-910はRV64GCをサポートしたRISC-Vプロセッサで、複数のカスタム拡張を持っており

- ビットマニピュレーション

- カスタムロード・ストア命令、TLBとキャッシュ操作命令

- v0.7.1をベースとしたRISC-Vベクトル拡張命令

- マルチコアおよびマルチクラスタでのSMPサポート

- Linuxブート

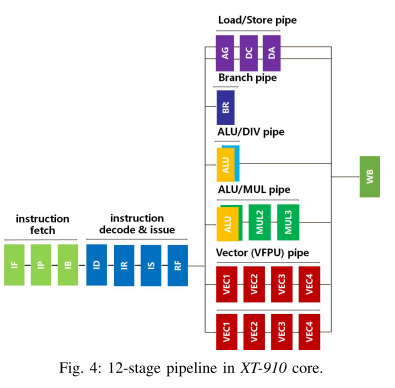

などの特徴を持っている。12ステージのアウトオブオーダ構成であり、TSMC 12nm FinFETにおいて2.5GHzで動作する。

- Xuantieシリーズの目的は、クラウドにインテグレーションするための次世代チップを設計すること。

Xuantie-910の仕様としては、

- RV64GCV (RV64GC + Vector)

- 50以上の独自拡張命令

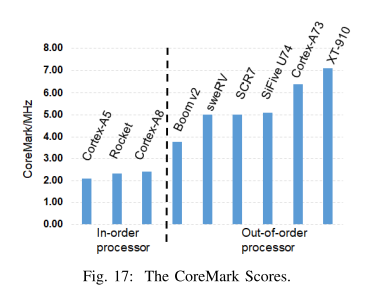

- Coremark/MHz = 7.1を達成

- ユーザモード・スーパバイザモード・マシンモードをサポート

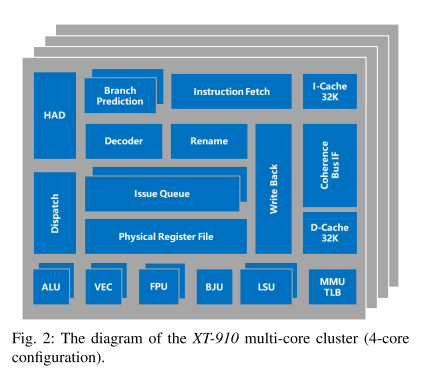

- クラスタを構成することができる。クラスタは4コアを1クラスタとして構成されている。

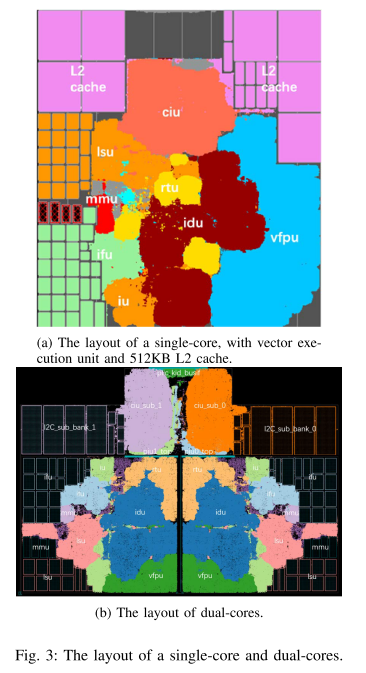

以下の図はTSMC 12nm FinFETプロセスでフロアプランを行った例。ターゲットは0.8V Vddで2.0GHz。LVTとULVT SRAMを使用している。もしULVTを使用して1.0V Vddを使用すると2.5GHzまで動作することができる。7nm FinFETを使用すると2.8GHzまで動作させることができる。

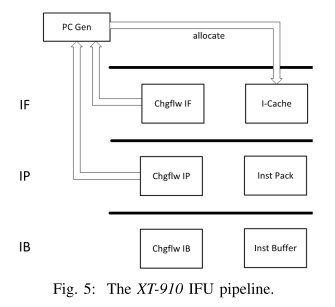

パイプライン構成は以下のようになっている。フロントエンドは7ステージの構成となっており、バックエンドは最大で8命令を発行することができ、必要パイプライン数は可変となっている。

Instruction Fetch Unit

命令フェッチユニットは3ステージパイプラインに分解される。

- 命令フェッチ(IF):L1キャッシュにアクセスして命令をフェッチする。128ビット分の命令をフェッチする。

- 命令パック(IP):命令のパックと前処理を行い、分岐のジャンプに関する処理を行う。また、キャッシュミスの処理を行う。後続のIDUが最大で3命令をデコードするので、IPステージがボトルネックとなる事は無い。

- 命令バッファ(IB):パッキングされた命令はバッファリングされる。最大で3命令がIDパイプラインに送られる。

XT-910の分岐予測は「ハイブリッドマルチモード分岐予測」と呼ばれており、分岐方向の予測と分岐アドレスの予測を行う。

「無条件分岐」「条件分岐」「インダイレクト分岐」「関数コールからのリターン」を予測する。すべてのプリフェッチした命令はIBUFに格納され、分岐予測に成功するとIBUFに格納されている命令は保持される。

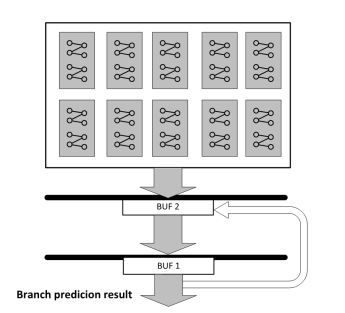

- 分岐方向の予測:XT-910は高速動作を行うが、SRAMの動作速度があまり速くないためSRAMから分岐予測をフェッチしてもどうしてもデータを取得するのに2サイクル消費される。これを解決するためにXT-910では分岐予測のメカニズムをマルチレベルバッファによるプリフェッチ機構により実現している。条件分岐命令の値をファジーマッチングパタンにより読み出し、BUF1とBUF2に格納する。分岐命令が検出されると、BUF1は予測に使用される。関連する値がBUF2からBUF1に移動され、次のサイクルの予測に使用される。

- 分岐アドレスの予測。分岐アドレスを予測するために、XT-910ではL1 BTBの以外にL0 BTBを使用する。L0 BTBはフルアソシアティブの16エントリのテーブルを持っており、もしこちらにヒットするとそのテーブルの値が次のアドレス予測に使用される。これにより分岐アドレスの予測時のパイプラインバブルが発生することを避ける。

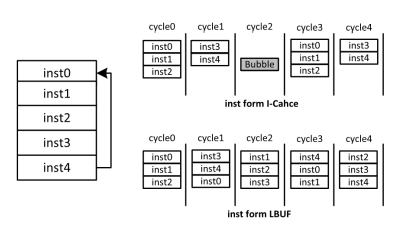

- ループバッファ:小さなループを検出するためにIFUにはループバッファ(LBUF)が実装されている。ループバッファ内にループコードがすべて入っていると、現在のループの最後の命令を、次のループの先頭と同時にフェッチすることができる。XT-910のループバッファは16エントリ保持している。

実行ステージ

バックエンドステージではID,IR, IS, RF, EX1-EX4, RT1-RT2パイプラインステージを持っている。

- IDU : IDからRFステージまで。IDステージは命令のデコードを行い、マイクロ命令に分解する。

- IRステージはGPR、FGPR、VGPRのリネームを行う。レジスタリネーミングはすべての汎用レジスタに対して行われる。

- ISステージはアウトオブオーダ命令のスケジューリングを行う。プロセッサは8つの命令スロットを持っており、すべての発行命令で共有されている。現在の実行可能なリソースとワークロードに応じて命令がロードされる。

- EXステージは8つのパイプラインを持っている。2つの算術演算ユニット、1つの分岐ユニット、1つのメモリユニット、2つのストアユニット、2つのスカラ浮動小数点・ベクトルユニットとなっている。

- RTステージは命令のライトバックとリタイアを管理する。RTU(Retirement Unit)は命令をリタイアさせ物理レジスタを開放する。プログラム実行の正確性を保証するため、命令はインオーダで完了される。

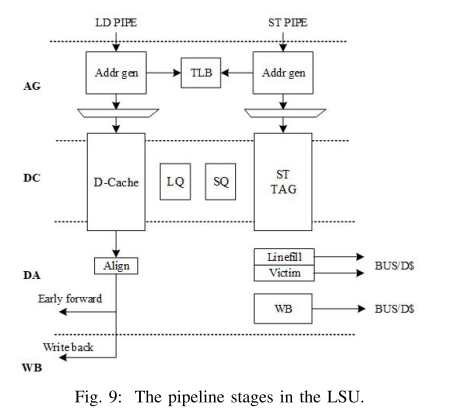

メモリサブシステム

デュアル発行のアウトオブオーダLSUを保持している。LSUの内部ではロードパイプとストアパイプが共存しており、パイプラインステージとしては「AG(Address Generation)」「DC(Data Cache)」「DA(Data Alignment)」「WB(Writeback)」から構成されている。AGステージではロード命令とストア命令がアドレスを生成し、uTLBにアクセスし仮想アドレスから物理アドレスに変換を行う。DCステージではロード命令とストア命令はデータキャッシュにアクセスする。DAステージではデータのアラインメントが行われる。最後にWBステージにて物理レジスタにデータが書き込まれる。

- ストア命令の実行を高速化するために、命令を実行する前にストア命令は2つのマイクロ命令に分割される。「st.addr」と「st.data」に分解される。st.addrはロードストアの共有命令キューから発行されるが、st.dataは専用の命令キューから発行され、物理レジスタファイルを読み込みデータを転送する。st.addrとst.dataはWBバッファでマージされる。

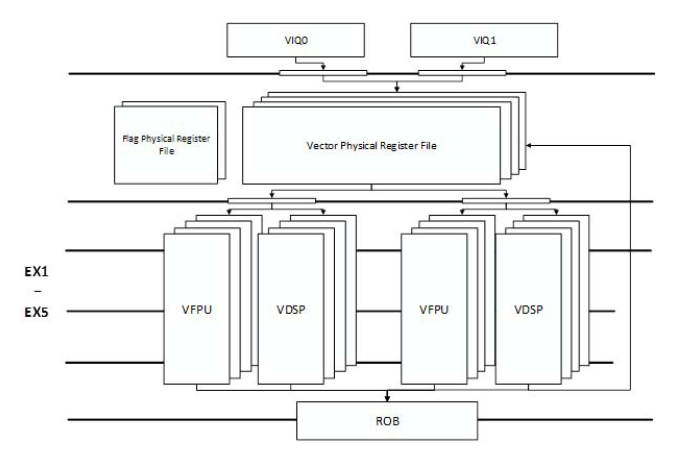

ベクトル命令

XT-910のベクトル命令はRISC-V Vector Extension v0.7.1に対応しており、デュアル発行を行うことができる。XT-910は64ビットのスカラパイプラインであるが、Vectorパイプラインは8ビットから64ビットまでのべ苦闘整数命令をサポートしており、浮動小数点命令では半制度から倍精度までの処理を実行することができる。ベクトルパイプラインは複数の独立したベクトルスライスから構成されている。各ベクトルスライスは完全に64ビットのデータパスで構成されており、マルチポートの64ビットのベクトル物理レジスタファイルと2つのアウトオブオーダベクトル実行ユニットを備えている。

各パイプラインは

各ベクトルスライスは独立したレジスタ、フォワーディングパス、実行データパスを持っている。

XT-910は64ビットから1024ビットまでのベクトル長をサポートすることができる。しかしパイプライン段数の多いアウトオブオーダのマルチコアプロセッサでは、ロード・ストアアクセスの最大アクセスビット数はバスとキャッシュアーキテクチャに依存している。したがttえ、2つのベクトルスライスではVLENとSLENの値を128ビットにすることが推奨されている。

性能

Coremarkスコアは7.1CMK/MHzとなっている。

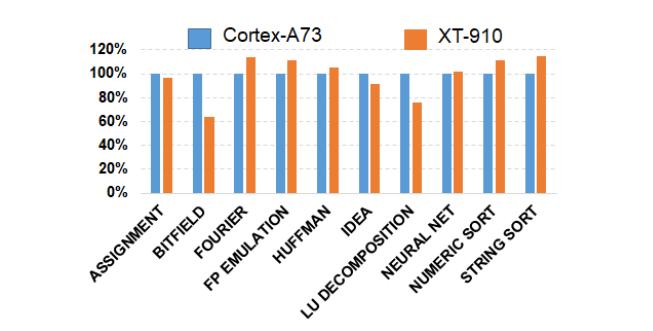

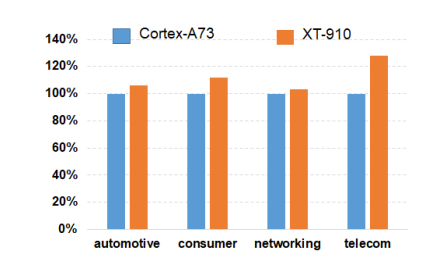

EEMBCの各種ベンチマークスコアの結果は、Cortex-A73に対して平均的に高いものになっている。

NBenchの性能は平均的にCortex-A73と同様に思える。