AWS F1インスタンス HDK の勉強を続けている。なかなか時間が取れなくて遅々として進まないが...

何か一つF1インスタンス向けに一つデザインを作って動かしてみたい。そのためには、DRAMのメモリアクセスを理解して実装できるようにならなければならない。

そのために、cl_dram_dmaデザインサンプルの波形を取得したいのだが、、うまく行かない。

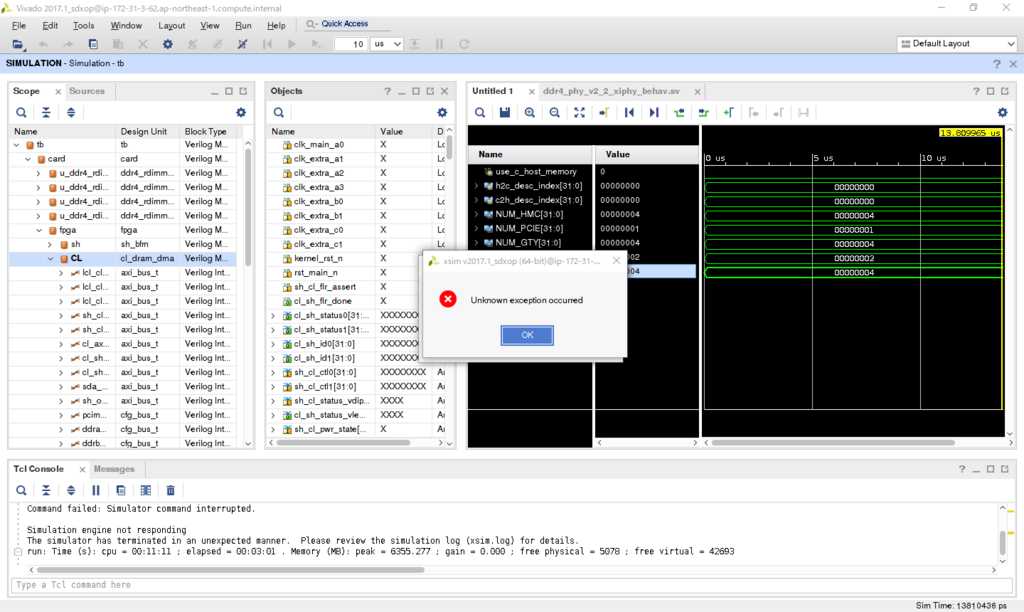

まず、これまでのようにVivadoシミュレータを使ったシミュレーションで、GUIを立ち上げて波形を取得しようとしたのだが、Vivado Simulatorが異常終了してしまった。

git diff Makefile.vivado waves.tcl diff --git a/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.vivado b/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.vivado index 972820f..2e50fb7 100644 --- a/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.vivado +++ b/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.vivado @@ -29,5 +29,5 @@ run: ifeq ($(TEST),test_null) cd $(SIM_DIR) && xsim -R -log $(C_TEST).log -tclbatch $(SCRIPTS_DIR)/waves.tcl tb else - cd $(SIM_DIR) && xsim -R -log $(TEST).log -tclbatch $(SCRIPTS_DIR)/waves.tcl tb + cd $(SIM_DIR) && xsim -R -log $(TEST).log -g -tclbatch $(SCRIPTS_DIR)/waves.tcl tb endif diff --git a/hdk/cl/examples/cl_dram_dma/verif/scripts/waves.tcl b/hdk/cl/examples/cl_dram_dma/verif/scripts/waves.tcl index 4b14d0d..706639e 100644 --- a/hdk/cl/examples/cl_dram_dma/verif/scripts/waves.tcl +++ b/hdk/cl/examples/cl_dram_dma/verif/scripts/waves.tcl @@ -24,4 +24,4 @@ if { [string length $curr_wave] == 0 } { } run 200 us -quit +# quit

make TEST=test_dram_dma

しかし諦めることはない。aws-fpgaリポジトリはそれ以外のシミュレータも対応している。 例えば、VCS / QuestaSim / IES に対応している。 私はVCSやIESは持っていないが、Quaestaならば Intel FPGA Starter Editionが無料で使えるではないか!どうにかこれで代用できないだろうか?

というわけ、Xilinxの環境にも関わらず、QuestaSim Intel FPGA Starter Editionをダウンロードしてインストールした。

インストール自体は普通に完了した。ただしいくつか正常に動作させるために足りていないといわれるパッケージをインストールしたり、QuestaSimのディレクトリでリンクを追加したりした。

$ cd ${HOME}/intelFPGA_lite/18.0/modelsim_ase $ ln -s linuxaloem linuxpe $ ln -s linuxaloem linux_x86_64pe

さらに、QuestaSimを動作させるために Makefile を以下のように変更した。

これでシミュレーションを実行する。

diff --git a/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.questa b/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.questa index 994d639..3480a42 100644 --- a/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.questa +++ b/hdk/cl/examples/cl_dram_dma/verif/scripts/Makefile.questa @@ -26,13 +26,13 @@ compile: $(COMPLIB_DIR) mkdir -p $(SIM_DIR) cd ${SIM_DIR} && ln -s -f ../questa_complib/modelsim.ini cd $(SIM_DIR) && vlog $(C_FILES) -ccflags "-I$(C_SDK_USR_INC_DIR)" -ccflags "-I$(C_SDK_USR_UTILS_DIR)" -ccflags "-I$(C_COMMON_DIR)" -ccflags "-DSV_TEST" -ccflags "-DSCOPE" -ccflags "-I$(C_INC_DIR)" - cd $(SIM_DIR) && vlog -mfcu -sv -64 -timescale 1ps/1ps -93 -L $(COMPLIB_DIR)/unisims_ver -L $(COMPLIB_DIR)/unimacro_ver -L $(COMPLIB_DIR)/secureip -f $(SCRIPTS_DIR)/top.$(SIMULATOR).f + cd $(SIM_DIR) && vlog -mfcu -sv -timescale 1ps/1ps -93 -L $(COMPLIB_DIR)/unisims_ver -L $(COMPLIB_DIR)/unimacro_ver -L $(COMPLIB_DIR)/secureip -f $(SCRIPTS_DIR)/top.$(SIMULATOR).f run: ifeq ($(TEST),test_null) - cd $(SIM_DIR) && vsim -c -voptargs="+acc" -64 -t ps -sv_seed random -L $(COMPLIB_DIR)/unisims_ver -L $(COMPLIB_DIR)/unisim -L $(COMPLIB_DIR)/unifast_ver -L $(COMPLIB_DIR)/unifast -L $(COMPLIB_DIR)/unimacro_ver -L $(COMPLIB_DIR)/unimacro -L $(COMPLIB_DIR)/secureip -L $(COMPLIB_DIR)/axi_register_slice_v2_1_12 -L $(COMPLIB_DIR)/axi_infrastructure_v1_1_0 -L $(COMPLIB_DIR)/axi_crossbar_v2_1_13 -L $(COMPLIB_DIR)/xpm -L $(COMPLIB_DIR)/axi_clock_converter_v2_1_11 -L $(COMPLIB_DIR)/fifo_generator_v13_1_4 -L $(COMPLIB_DIR)/axi_data_fifo_v2_1_11 -L $(COMPLIB_DIR)/generic_baseblocks_v2_1_0 -l $(C_TEST).log -do "run -all; quit -f" tb glbl $(TEST) + cd $(SIM_DIR) && vsim -c -voptargs="+acc" -t ps -sv_seed random -L $(COMPLIB_DIR)/unisims_ver -L $(COMPLIB_DIR)/unisim -L $(COMPLIB_DIR)/unifast_ver -L $(COMPLIB_DIR)/unifast -L $(COMPLIB_DIR)/unimacro_ver -L $(COMPLIB_DIR)/unimacro -L $(COMPLIB_DIR)/secureip -L $(COMPLIB_DIR)/axi_register_slice_v2_1_12 -L $(COMPLIB_DIR)/axi_infrastructure_v1_1_0 -L $(COMPLIB_DIR)/axi_crossbar_v2_1_13 -L $(COMPLIB_DIR)/xpm -L $(COMPLIB_DIR)/axi_clock_converter_v2_1_11 -L $(COMPLIB_DIR)/fifo_generator_v13_1_4 -L $(COMPLIB_DIR)/axi_data_fifo_v2_1_11 -L $(COMPLIB_DIR)/generic_baseblocks_v2_1_0 -l $(C_TEST).log -do "run -all; quit -f" tb glbl $(TEST) else - cd $(SIM_DIR) && vsim -c -voptargs="+acc" -64 -t ps -sv_seed random -L $(COMPLIB_DIR)/unisims_ver -L $(COMPLIB_DIR)/unisim -L $(COMPLIB_DIR)/unifast_ver -L $(COMPLIB_DIR)/unifast -L $(COMPLIB_DIR)/unimacro_ver -L $(COMPLIB_DIR)/unimacro -L $(COMPLIB_DIR)/secureip -L $(COMPLIB_DIR)/axi_register_slice_v2_1_12 -L $(COMPLIB_DIR)/axi_infrastructure_v1_1_0 -L $(COMPLIB_DIR)/axi_crossbar_v2_1_13 -L $(COMPLIB_DIR)/xpm -L $(COMPLIB_DIR)/axi_clock_converter_v2_1_11 -L $(COMPLIB_DIR)/fifo_generator_v13_1_4 -L $(COMPLIB_DIR)/axi_data_fifo_v2_1_11 -L $(COMPLIB_DIR)/generic_baseblocks_v2_1_0 -l $(TEST).log -do "run -all; quit -f" tb glbl $(TEST) + cd $(SIM_DIR) && vsim -c -voptargs="+acc" -t ps -sv_seed random -L $(COMPLIB_DIR)/unisims_ver -L $(COMPLIB_DIR)/unisim -L $(COMPLIB_DIR)/unifast_ver -L $(COMPLIB_DIR)/unifast -L $(COMPLIB_DIR)/unimacro_ver -L $(COMPLIB_DIR)/unimacro -L $(COMPLIB_DIR)/secureip -L $(COMPLIB_DIR)/axi_register_slice_v2_1_12 -L $(COMPLIB_DIR)/axi_infrastructure_v1_1_0 -L $(COMPLIB_DIR)/axi_crossbar_v2_1_13 -L $(COMPLIB_DIR)/xpm -L $(COMPLIB_DIR)/axi_clock_converter_v2_1_11 -L $(COMPLIB_DIR)/fifo_generator_v13_1_4 -L $(COMPLIB_DIR)/axi_data_fifo_v2_1_11 -L $(COMPLIB_DIR)/generic_baseblocks_v2_1_0 -l $(TEST).log -do "add log -r sim:/tb/card/fpga/CL/*; run -all" tb glbl $(TEST) endif $(COMPLIB_DIR):

シミュレーションを実行すると、以下で固まってしまった。Vivado Simulator (のGUIなし)だと、ちゃんと進むのに...

make TEST=test_dram_dma QUESTA=1 # Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.CL.SH_DDR.<protected>.<protected>.<protected>.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[8].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref # Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.CL.SH_DDR.<protected>.<protected>.<protected>.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[7].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref # Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.CL.SH_DDR.<protected>.<protected>.<protected>.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[6].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref # Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.CL.SH_DDR.<protected>.<protected>.<protected>.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[5].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref # Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.CL.SH_DDR.<protected>.<protected>.<protected>.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[4].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref # Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.CL.SH_DDR.<protected>.<protected>.<protected>.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[3].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref

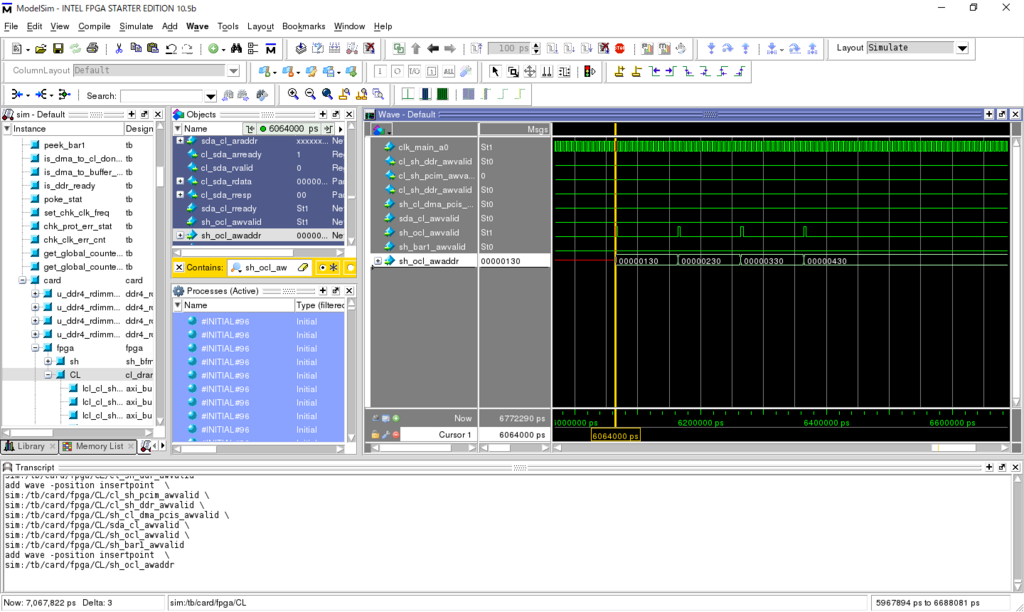

GUIを立ち上げてみた。とりあえずシミュレーションは進んでいるようだが、まったく終わらない... 一応波形は取れているようだが、Vivado Simulationに比べて非常に遅い。何故だ?