AWS F1インスタンス HDK の勉強を続けている。なかなか時間が取れなくて遅々として進まないが...

HDKのサンプルプログラムは、当然だがF1インスタンスのFPGAを前提にしている。 つまり Xilinx の VU9Pだ。 ところが、このFPGAは私のような貧乏な個人が所有しているVivado WebPackでは論理合成できないし、DDR4のIPも使用することができない。 F1インスタンス以外のAWSの構成を使用して、AMI FPGA Marketplaceを使用することでとりあえずこの問題は解決できる。 しかし、その間中ずっとAWSの料金は発生しているし、料金が発生する割にVU9P専用のIPを使っているわけでもなく、簡単なデザインを試行しているだけにすぎない。 なんとかしてデザインの構成を書き換えて、手元のローカルPCで、Vivado WebPackを使って実行できるように改造できないだろうか?

VU9Pを使う場合の問題点はただ一つ。手元でシミュレーションを行う場合にDDR4のIPコアを使用することができない。 まずは、 ./hdk_setup.sh を source するときに以下のエラーメッセージが表示される。 これにより、 Xilinx の DDR4 のIPを生成することができない?らしい。

msyksphinz@msyksphinz-VirtualBox:~/work/aws-fpga-msyksphinz$ source ./hdk_setup.sh INFO: Setting up environment variables INFO: Using Vivado v2017.1 (64-bit) INFO: Using HDK shell version shell_v071417d3 INFO: HDK shell's SH_CL_BB_routed.dcp hasn't been downloaded yet. INFO: Downloading latest HDK shell SH_CL_BB_routed.dcp from aws-fpga-hdk-resources/hdk/shell_v071417d3/build/checkpoints/from_aws/SH_CL_BB_routed.dcp INFO: HDK shell is up-to-date INFO: HDK shell's cl_hello_world.debug_probes.ltx hasn't been downloaded yet. INFO: Downloading latest HDK shell cl_hello_world.debug_probes.ltx from aws-fpga-hdk-resources/hdk/shell_v071417d3/build/debug_probes/from_aws/cl_hello_world.debug_probes.ltx INFO: HDK shell is up-to-date INFO: HDK shell's cl_dram_dma.debug_probes.ltx hasn't been downloaded yet. INFO: Downloading latest HDK shell cl_dram_dma.debug_probes.ltx from aws-fpga-hdk-resources/hdk/shell_v071417d3/build/debug_probes/from_aws/cl_dram_dma.debug_probes.ltx INFO: HDK shell is up-to-date INFO: DDR4 model files in /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/models/ddr4_model/ do NOT exist. Running model creation step. INFO: Building in /home/msyksphinz/work/aws-fpga-msyksphinz/ddr4_model_build INFO: This could take 5-10 minutes, please be patient! /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.sh: 18: /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.sh: [[: not found /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.sh: 23: /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.sh: [[: not found /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.sh: 29: /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.sh: [[: not found ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:54:47 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source /home/msyksphinz/work/aws-fpga-msyksphinz/hdk/common/verif/scripts/init.tcl # set_msg_config -severity INFO -suppress # set_msg_config -severity STATUS -suppress # set_msg_config -severity WARNING -suppress CRITICAL WARNING: [Common 17-1355] You are suppressing all messages of type 'WARNING'. You may potentially disregard important DRC, CDC, and implementation messages that can negatively impact your design. If this is not desired, please run 'reset_msg_config -suppress -severity {WARNING}' to undo this change. # set_msg_config -string {exportsim} -suppress # set_msg_config -string {IP_Flow} -suppress # create_project -force tmp_ddr ./tmp -part xcvu9p-flgb2104-2-i ERROR: [Coretcl 2-106] Specified part could not be found. ERROR: DDR4 model build failed. ERROR: Build dir=/home/msyksphinz/work/aws-fpga-msyksphinz/ddr4_model_build

方法その1試行. FPGAのチップ名を書き換えてVivado WebPackでも実行できるように改造する

まず試行したのが、 F1インスタンスで使用されているVU9Pを使用するのではなく、WebPackでも使用できる規模の小さなFPGAを使用して、Vivado Simulatorを動かすことができないか、ということだ。

DDR4のIPを調べてみた。また、Vivado WebPackを立ち上げて、使用可能なFPGAデバイスを調査した。

$ vivado -mode tcl Vivado% get_parts -regexp xcku3p.* xcku3p-ffva676-1-e xcku3p-ffva676-1-i xcku3p-ffva676-1L-i xcku3p-ffva676-1LV-i xcku3p-ffva676-2-e xcku3p-ffva676-2-i xcku3p-ffva676-2L-e xcku3p-ffva676-2LV-e xcku3p-ffva676-3-e xcku3p-ffvb676-1-e xcku3p-ffvb676-1-i xcku3p-ffvb676-1L-i xcku3p-ffvb676-1LV-i xcku3p-ffvb676- 2-e xcku3p-ffvb676-2-i xcku3p-ffvb676-2L-e xcku3p-ffvb676-2LV-e xcku3p-ffvb676-3-e xcku3p-ffvd900-1-e xcku3p-ffvd900-1-i xcku3p-ffvd900-1L-i xcku3p-ffvd900-1LV-i xcku3p-ffvd900-2-e xcku3p-ffvd900-2-i xcku3p-ffvd900-2L-e xcku3p-ffvd900-2LV-e xcku3p-ffvd900-3-e xcku3p-sfvb 784-1-e xcku3p-sfvb784-1-i xcku3p-sfvb784-1L-i xcku3p-sfvb784-1LV-i xcku3p-sfvb784-2-e xcku3p-sfvb784-2-i xcku3p-sfvb784-2L-e xcku3p-sfvb784-2LV-e xcku3p-sfvb784-3-e

Kintex のFPGAが使用できそうだ。 そこで、AWS-FPGAのリポジトリ中のtclやスクリプトなどをすべて書き換えて、WebPackでも使用可能なデザインを作成してみる。

sed -i 's/xcvu9p-flgb2104-2-i/xcku3p-sfvb784-3-e/g' `ag -l xcvu9p-flgb2104-2-i`

これでHDKディレクトリのhdk/example/cl_hello_world を実行してみたのだが、やはりDDR4のIP生成で失敗し、WebPackでは実行することができなかった。 この方法は失敗だ。

方法その2試行. DDR4 のデザインを削除する

では、とりあえずDD4を使用しないデザインであれば、DDR4のテストモデルを削除することでWebPackのシミュレータを動かすことはできないだろうか。 DDR4を使用するデザインはすべて動かなくなるが、簡単なデザインならテストできるはずだ。

そこで、hdk の デザインからDDR4のモデルをすべて削除してみることにした。 以下のようにデザインを書き換える。

$ git st On branch master Your branch is up-to-date with 'origin/master'. Changes not staged for commit: (use "git add <file>..." to update what will be committed) (use "git checkout -- <file>..." to discard changes in working directory) modified: hdk/cl/examples/cl_dram_dma/verif/scripts/top.vivado.f modified: hdk/cl/examples/cl_hello_world/verif/scripts/top.vivado.f modified: hdk/common/verif/models/fpga/fpga_ddr.svh modified: hdk/common/verif/tb/filelists/ddr.vivado.f modified: hdk/supported_vivado_versions.txt no changes added to commit (use "git add" and/or "git commit -a")

hdk/supported_vivado_versions.txtこれは 通常のVivadoも使用できるようにするための変更だ。

--- a/hdk/supported_vivado_versions.txt +++ b/hdk/supported_vivado_versions.txt @@ -1,2 +1,3 @@ Vivado v2017.1_sdx (64-bit) Vivado v2017.1_sdxop (64-bit) +Vivado v2017.1 (64-bit)

hdk/cl/examples/cl_dram_dma/verif/scripts/top.vivado.f若干面倒なのだが、define を作って、特殊環境ではDDR4のコアを削除するように変更する。

--- a/hdk/cl/examples/cl_dram_dma/verif/scripts/top.vivado.f +++ b/hdk/cl/examples/cl_dram_dma/verif/scripts/top.vivado.f @@ -14,6 +14,7 @@ # limitations under the License. --define VIVADO_SIM +--define __MSYKSPHINZ_USE_DDR4__ --sourcelibext .v --sourcelibext .sv

hdk/cl/examples/cl_hello_world/verif/scripts/top.vivado.f

--- a/hdk/cl/examples/cl_hello_world/verif/scripts/top.vivado.f +++ b/hdk/cl/examples/cl_hello_world/verif/scripts/top.vivado.f @@ -14,6 +14,7 @@ # limitations under the License. -define VIVADO_SIM +-define __MSYKSPHINZ_USE_DDR4__ -sourcelibext .v -sourcelibext .sv

--- a/hdk/common/verif/models/fpga/fpga_ddr.svh +++ b/hdk/common/verif/models/fpga/fpga_ddr.svh @@ -156,6 +156,8 @@ assign CLK_300M_DIMM3_DP = ddr_clk; assign CLK_300M_DIMM3_DN = ~ddr_clk; +`ifndef __MSYKSPHINZ_USE_DDR4__ + `ifndef QUESTA_SIM `ifndef IES_SIM //------------------------------------------------------ @@ -482,3 +484,5 @@ .bfunc(), .vddspd()); + +`endif // __MSYKSPHINZ_USE_DDR4__

hdk/common/verif/tb/filelists/ddr.vivado.fさらに、生成できなかったDDR4のIPをファイルリストから外す。

--- a/hdk/common/verif/tb/filelists/ddr.vivado.f +++ b/hdk/common/verif/tb/filelists/ddr.vivado.f @@ -110,4 +110,5 @@ ${XILINX_IP}/ddr4_core/tb/microblaze_mcs_0.sv --sourcelibdir ${HDK_COMMON_DIR}/verif/models/ddr4_rdimm_wrapper # ${HDK_COMMON_DIR}/verif/models/ddr4_rdimm_wrapper/ddr4_rdimm_wrapper.sv -${HDK_COMMON_DIR}/verif/models/ddr4_model/ddr4_sdram_model_wrapper.sv + +# ${HDK_COMMON_DIR}/verif/models/ddr4_model/ddr4_sdram_model_wrapper.sv

cl_hello_world のシミュレーションを実行すると、無事にPassできることが分かった。

~/work/aws-fpga-msyksphinz/hdk/cl/examples/cl_hello_world/verif/scripts$ make TEST=test_hello_world ... WARNING: Behavioral models for independent clock FIFO configurations do not model synchronization delays. The behavioral models are functionally correct, and will represent the behavior of the configured FIFO. See the FIFO Generator User Guide for more information. WARNING: Behavioral models for independent clock FIFO configurations do not model synchronization delays. The behavioral models are functionally correct, and will represent the behavior of the configured FIFO. See the FIFO Generator User Guide for more information. WARNING: Behavioral models for independent clock FIFO configurations do not model synchronization delays. The behavioral models are functionally correct, and will represent the behavior of the configured FIFO. See the FIFO Generator User Guide for more information. Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[3].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[4].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[5].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[6].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[7].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[8].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[9].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[10].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref Info: [Unisim HPIO_VREF-1] Fabric Tune Value changed to 0011101. Instance: tb.card.fpga.sh.DDR4_3.inst.u_ddr4_mem_intfc.u_mig_ddr4_phy.inst.u_ddr_iob.genByte[11].u_ddr_iob_byte.genblk1.genVref.u_hpio_vref value of vdip:0 Writing 0xDEAD_BEEF to address 0x00000500 Reading 0xefbeadde from address 0x00000500 TEST PASSED Reading 0x0000beef from address 0x00000504 TEST PASSED value of vled:0 $finish called at time : 5330 ns : File "/home/msyksphinz/work/aws-fpga-msyksphinz/hdk/cl/examples/cl_hello_world/verif/tests/test_hello_world.sv" Line 67 $

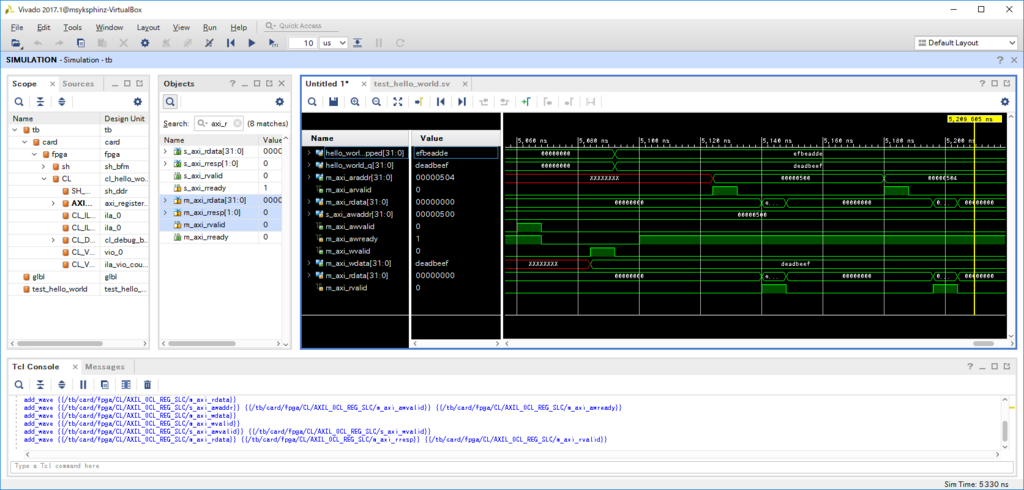

一応GUIも立ち上げて、波形を確認した。正しく動いているようだ。

ただし、DDR4を使用する test_dma_dram は動かない。

~/work/aws-fpga-msyksphinz/hdk/cl/examples/cl_dram_dma/verif/scripts$ make TEST=test_hello_world ... [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43920 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43921 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43922 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43923 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43924 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43925 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43926 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43927 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43928 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:43929 read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:4392a read data is: 0 [ 37082000] : *** ERROR *** DDR3 Data mismatch, addr:4392b read data is: 0 [ 37402000] : *** ERROR *** DDR0 Data mismatch, addr:1 read data is: 0 [ 37722000] : *** ERROR *** DDR1 Data mismatch, addr:400000000 read data is: 0 [ 38062000] : *** ERROR *** DDR2 Data mismatch, addr:800000005 read data is: 0 [ 38382000] : *** ERROR *** DDR3 Data mismatch, addr:c00000000 read data is: 0 [ 38982000] : Checking total error count... [ 38982000] : Detected 6560 errors during this test [ 38982000] : *** TEST FAILED *** $finish called at time : 38982 ns : File "/home/msyksphinz/work/aws-fpga-msyksphinz/hdk/cl/examples/cl_dram_dma/verif/tests/test_dram_dma.sv" Line 264 run: Time (s): cpu = 00:00:00.90 ; elapsed = 00:04:55 . Memory (MB): peak = 1042.570 ; gain = 0.000 ; free physical = 2283 ; free virtual = 10164 ## quit INFO: [Common 17-206] Exiting xsim at Sat May 5 00:17:39 2018... $