- 作者: John L. Hennessy,David A. Patterson

- 出版社/メーカー: Morgan Kaufmann

- 発売日: 2017/12/07

- メディア: ペーパーバック

- この商品を含むブログを見る

7.3章はがっつりディープニューラルネットワークの内容だ。今回はMicrosoft Catapult, フレキシブルなデータセンタアクセラレータ。

目次

- 7.1章 イントロダクション

- 7.2章 DSAのガイドライン

- 7.3章 DSAの用語集

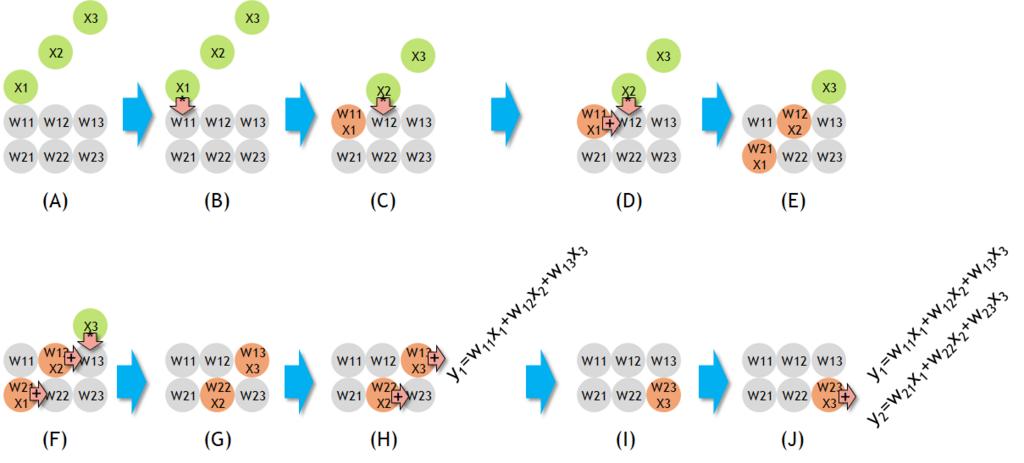

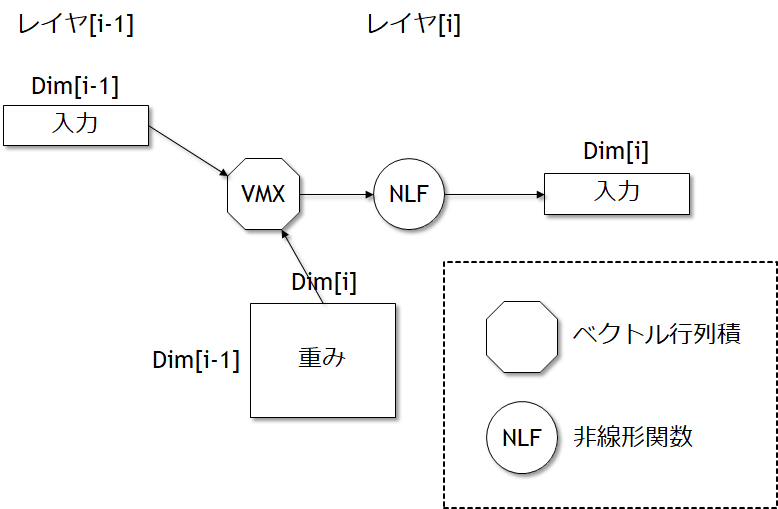

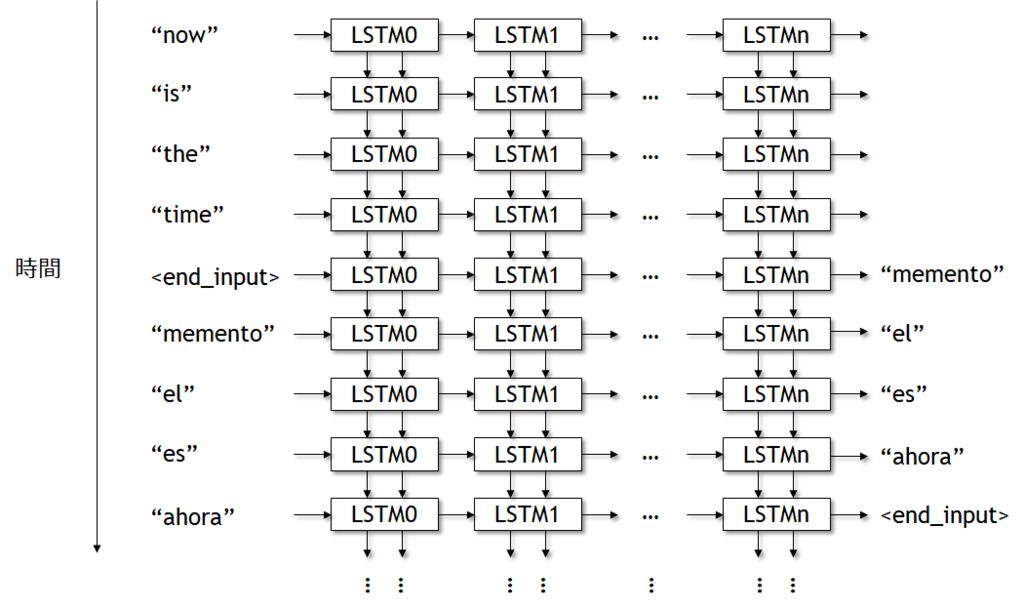

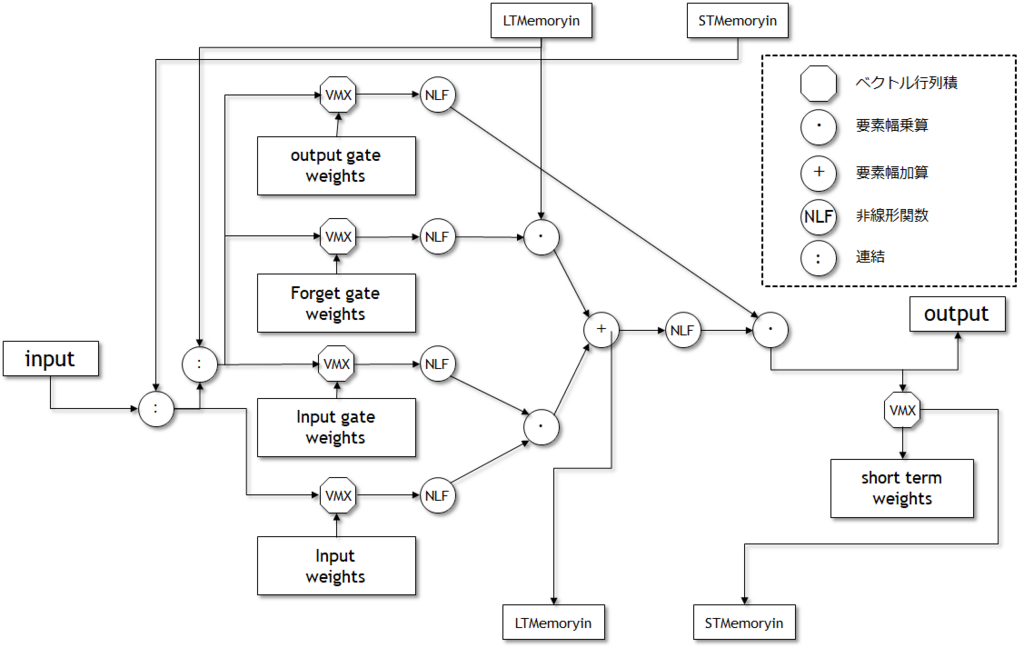

- 7.3章 DNNのニューロン・トレーニングと推論

- 7.3章 多層パーセプトロン、畳み込みニューラルネットワーク、再帰型ニューラルネットワーク

- 7.4章 Google's Tensor Processing Unit

- 7.5章 Microsoft Catapult, フレキシブルなデータセンタアクセラレータ

- 7.6章 Intel Crest, 学習のためのデータセンタアクセラレータ

- 7.7章 Pixel Visual Core, パーソナルモバイル画像処理ユニット)

これは著者が読んだ内容をまとめているだけなので、誤訳、理解不足により誤っている可能性があります!鵜呑みにしないようにお願いします。

7.5 Microsoft Catapult, フレキシブルなデータセンタアクセラレータ

GoogleがカスタムASICをデータセンタにデプロイすることを考えているまさにその時、Microsoftは彼らのためのアクセラレータについて考えていた。 Microsoftの視点は、以下のガイドラインに沿った解決策を考えることであった。

- マシンの短期間での再デプロイを可能にするためにサーバのホモジニアス性を保持する必要があり、より複雑なマシンメンテナンスとスケジューリングが発生する必要を避ける必要がある。そのことがDSAにとって少し奇妙なことであっても、この方針を維持する必要があった。

- すべてのアプリケーションを複数のアプリケーションに焼きこまずに単一のアクセラレータを使用するよりも、多くのリソースが必要なアプリケーションにとってスケーリングができる必要があった。

- 電力性能が必要だった。

- ある一か所で問題が発生しても、ディペンダビリティの問題が発生しないようにする必要があった。

- 既存のサーバに対して、スペース的な問題と電力的な問題がうまくフィットする必要があった。

- データセンタのネットワーク性能と信頼性を低下させない必要があった。

- アクセラレータはサーバのコストパフォーマンスを向上させる必要があった。

最初のループは、ASICをデプロイするとサーバ上で動作するいくつかのアプリケーションにのみ限定される。これはGoogleが選択したケースである。

MicrosoftはCatapultというプロジェクトをスタートさせ、PCIeバスを搭載したFPGAボードをデータセンタサーバに設置した。 これらのボードは複数のFPGAが動作するのに必要なネットワーク能力を持っていた。 FPGAのフレキシビリティを使用して複数のアプリケーションを異なるサーバ上で使用し、同じサーバ上でリプログラミングして異なるアプリケーションプログラムを高速化させる、という計画である。 このアクセラレータによる恩恵を増大させた。 FPGAのもう一つの利点はASICよりもNREが低いことであり、投資の恩恵を増大させることができる。 私たちはCatapultによる2つのジェネレータについて評価を行い、WSCの必お由奈性能をどのようにして満たすのかについて議論を行った。

FPGAの一つの面白い特徴として、各アプリケーション~あるいはアプリケーションの各フェーズですら~一つのDSAとして考えることができるということである。 したがって本節では、1つのハードウェアプラットフォーム上で多くの優れたアーキテクチャの例について見ていくことができる。

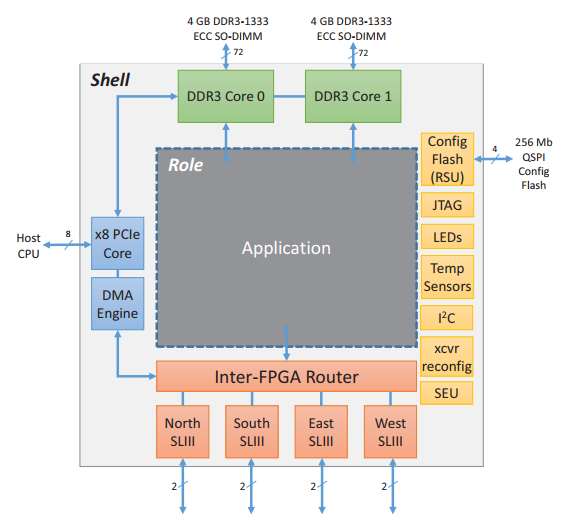

Catapultの実装とアーキテクチャ

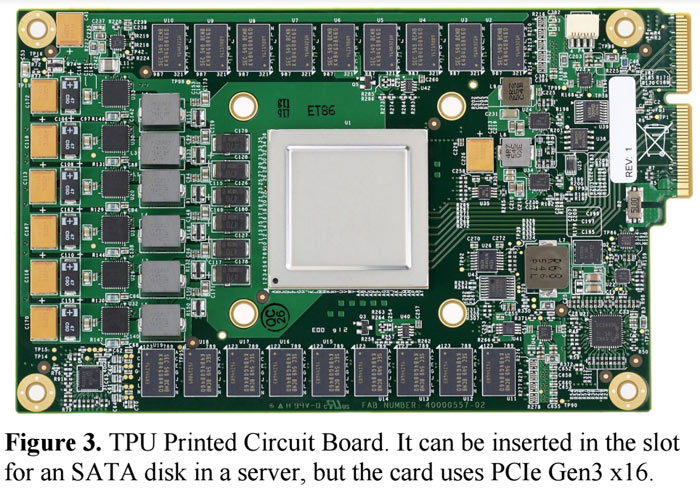

図7.19はMicrosoftが彼らのサーバに適合するように設計したPCIeボードである。 電力のことを考えて25Wで設計してある。 この制約により、最初のCatapultの実装ではFPGAはAlteraのStratix V D5 FPGAに限定された。 このボードは32MBのフラッシュメモリを装備しており、2バンクのDDR3-1600 DRAMを持ち8GBの容量を持っていた。 FPGAは3926個の16bit ALUを持っており、5MBのオンチップメモリを持っていた。またDDR3 DRAMとの接続バンド幅は11GB/sであった。

図7.19 Catapultのボード設計 (https://www.microsoft.com/en-us/research/wp-content/uploads/2016/02/Catapult_ISCA_2014.pdf より抜粋)

データセンタのラックの半分である48個のサーバにCatapultのボードが実装された。 Catapultは、複数のFPGAアプリケーションに対してデータセンタのネットワークに影響を与えないというガイドラインに従っている。 独立した低レイテンシの20Gbit/sのネットワークによって48個のFPGAを接続した。 ネットワークのトポロジは6×8のトーラスネットワークであった。

一か所の故障により全体が影響を与えないというガイドラインに従うため、このネットワークは1つのFPGAが故障しても再構成できるようになっている。 ボードは、FPGAより外部のすべてのメモリに対してSECDED保護がかけられており、非常に大きなデータセンタに対してもデプロイが可能になっている。

プログラマビリティを確保するためにFPGAはチップ上のメモリを利用しているため、プロセスの進化に伴う放射線の影響により、ASICに比べてSingle-event upsets(SEUs)に対して脆弱である。 Catapultで使用しているボードのAltera FPGAは、FPGA内部にSEUを検出して訂正するメカニズムを実装しており、FPGAのコンフィグレーション状態が切り替わるときにSEUにより問題が発生する可能性を削減している。

独立したネットワークを追加することにより、データセンタネットワークと比較して、通信性能が変動する可能性を防いでいる。 ネットワークは予期せずそのレイテンシが増加することがある。これは特にエンドユーザが使用するアプリケーションにとって有害なものとなる。 したがって分離されたネットワークによりCPUからアクセラレータに、簡単にタスクをオフロードできるようになっている。 このFPGAネットワークは、エラー率がデータセンタのプロトコルよりも低く、トポロジがうまく定義されているため、データセンタのプロトコルよりもより簡単なもので動作するようになっている。

FPGAを再コンフィグレーションする場合には弾力性について考慮する必要があり、隣接するノードが故障やクラッシュを起こしてもホストサーバや隣接するノードが巻き込まれないようにする必要がある。 Microsoftは高レベルなプロトコルを開発し、複数のFPGAが再構成する場合でも安全性を保証している。

Catapultのソフトウェア

CatapultとTPUの最も大きな違いがあるとすれば、プロ蔵身をVerilogもしくはVHDLで記述するというところである。 Catapultの著者が書いているように(Putnam et al., 2016):

ゆくゆくは、データセンタにFPGAを幅広く適用するための最も大きな障害はプログラマビリティになるだろう。FPGAの開発は、幅広いレジスタトランスファレベルのハンドコーディングや、マニュアルチューニングが必要である。

Catapult FPGAのプログラマビリティの問題を削減するために、図7.20に示すようにレジスタトランスファレベル(Register Transfer Level:RTL)のコードを「シェル(shell)」と「ロール(role)」に分割した。

シェルのコードは、組み込みCPUで動作するライブラリのようなものである。 シェルには、同じFPGAボード上で、データの整列、CPUとFPGAの通信、FPGAとFPGAの通信、データの移動、再コンフィグレーション、モニタリング、などのアプリケーションを通して再利用することのできるRTLコードが含まれている。 シェルのRTLコードはAlteraのFPGA上で23%を占めている。 ロールのコードはアプリケーションの論理で、Catapultのプログラマは残りの77%のFPGAのリソースを使用して記述する。 シェルは標準APIや、アプリケーションの標準的な動作のような役割を持っている。

図7.20 Catapultのコンポーネントである、シェルとロールによりRTLコードが分割される(https://www.microsoft.com/en-us/research/wp-content/uploads/2016/02/Catapult_ISCA_2014.pdf より抜粋)

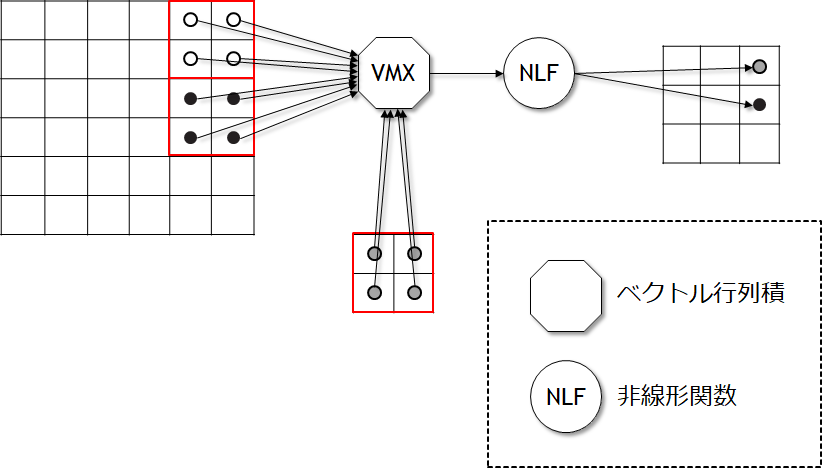

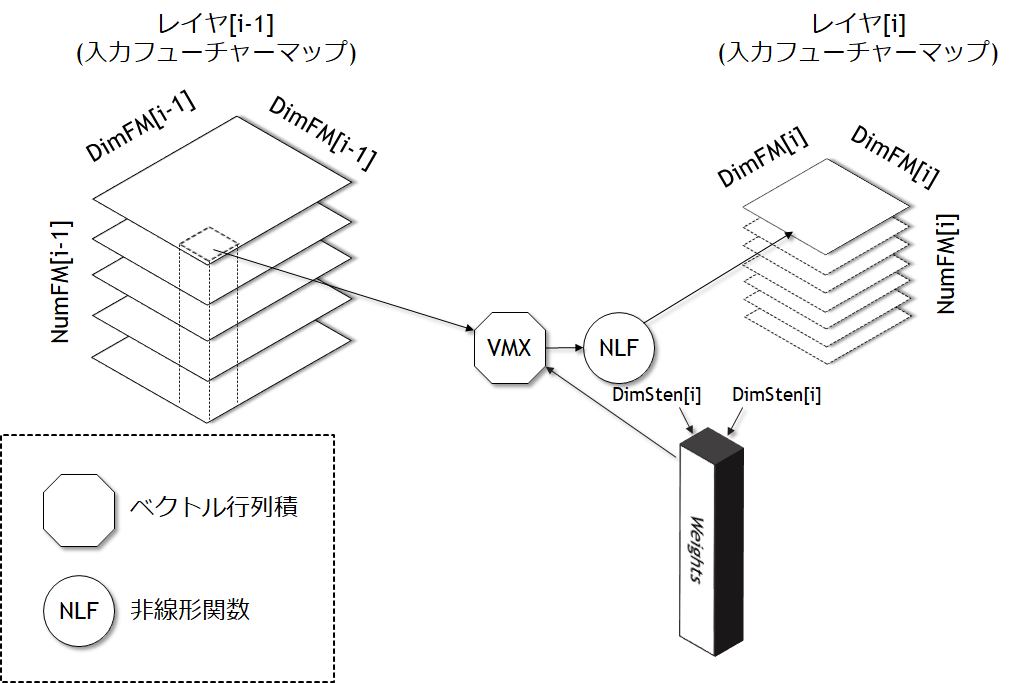

Catapult上でのCNN

MicrosoftはCatapult向けにコンフィギャラブルなCNNアクセラレータを開発した。 コンフィグレーションのパラメータにはニューラルネットワークのレイヤと、それらのレイヤの次元、そして計算精度なども含まれている。 図7.2はCNNアクセラレータのブロックダイアグラムである。 カギとなる特徴は、

- ランタイムに構成を変更することができるデザインである。FPGAのツールを利用して再コンパイルする必要はない。

- メモリアクセスを最小化するために、CNNデータ構造を効率的にバッファしている。

- Processing Element(PE)の2次元アレイを、数千のユニットまでスケーリングすることができる。

図7.21 Catapult向けのCNNアクセラレータ (https://www.microsoft.com/en-us/research/wp-content/uploads/2014/06/HC27.25.432-Catapult_HOTCHIPS2015_Chung_DRAFT_V8.pdf より抜粋)

画像はDRAMに転送され、FPGA中の複数バンクのバッファに入力される。 入力値は複数のPEに転送され、特徴マップを出力するためにステンシルが計算される。 図7.21左上のコントローラにより各PEのデータフローを制御する。 最終結果はCNNの次のレイヤで再利用するために、入力バッファに再挿入される。

TPUの様に、PEはシストリックアレイの形式で設計されている。 図7.22はPEのデザインの詳細である。

図7.22 Catapult向けCNNアクセラレータのProcessing Element(PE)のデザイン (https://www.microsoft.com/en-us/research/wp-content/uploads/2014/06/HC27.25.432-Catapult_HOTCHIPS2015_Chung_DRAFT_V8.pdf より抜粋)

Catapultによる検索の高速化

Catapultによる投資の効果を、評価するための主要なアプリケーションは、Microsoftの検索エンジンであるBingの中心となるアプリケーションである「ランキング」と呼ばれる処理である。 ランキングは、検索からその結果をランク付けする機能である。 その結果はドキュメントのスコアでありウェブページ上のドキュメントの位置づけであり、この情報がユーザに提示される。 アルゴリズムは3つのステージを踏む。

- 特徴抽出: ドキュメント中から、サーチクエリという情報に基づいて何千という興味深い特徴を抽出する。例えば、クエリのフレーズがドキュメント中に何度登場したかなどの情報である。

- 自由形式表現 : 1.の情報に基づいて、何千もの特徴の組み合わせを計算する。

- 機械学習スコアリング : 機械学習のアルゴリズムを利用して、1.2.のステージの情報を評価しドキュメントの浮動小数点のスコアを計算する。このスコアがホストのサーチソフトウェアに返される。

ランキングのCatapult実装では、Bingのソフトウェアと同一の結果が得られた。それどころか、既存のソフトウェアのバグまで再現した!

前述したガイドラインの1つの恩恵を得るために、ランキングの関数は単一のFPGAにフィットする必要はない。 ランキングのステージは、以下のようにして8つのFPGAに分割された。

- 1つのFPGAを用いて特徴抽出を実装する。

- 2つのFPGAを用いて自由形式表現を実装する。

- 1つのFPGAを使って圧縮ステージを実装し、スコアエンジンの効率を向上させる。

- 3つのFPGAを使って、機械学習によるスコアリングを行う。

残りの1つのFPGAは、故障時に対応するための予備である。 1つのアプリケーションに対して複数のFPGAを使用しても、専用のFPGAネットワークを構築しているためにうまく動作させることができた。

図7.23は特徴抽出のステージの構成を示している。 43個の特徴抽出のためのステートマシンを実装しており、ドキュメントとクエリのペアに対して並列に4500個の特徴を抽出している。

図7.23 特徴抽出ステージのFPGA実装のアーキテクチャ

次に、自由形式表現のステージである。 ゲートやステートマシンを実装するのではなく、Microsoftは60コアのプロセッサを実装し、マルチスレッドによる長いレイテンシを隠ぺいした。 GPUとは異なり、MicrosoftのプロセッサはSIMD実行は必要なかった。 このプロセッサはレイテンシが重要となるターゲットに対して以下の3つの特徴を持っていた。

- 書くコアは4つの同時スレッデングを持っており、1つのスレッドがレイテンシが長い処理によりストールしても他のスレッドが動作するようになっていた。すべての機能ユニットがパイプライン化され、新しい処理を毎サイクル実行することができた。

- スレッドはプライオリティエンコーダにより性的に優先度がつけられていた。最もレイテンシ長い表現は、すべてのコアにおいてスレッドのスロット0を使用する。次に遅い表現はすべてのコアにおいてスレッド1を使用した。

- 自由形式表現を使用するために、表現データが多すぎて同時に一つのFPGAにフィットしない場合は2つのFPGAに分割することができた。

FPGAにおける再プログラマブル可能なシステムの1つの負荷は、あまり動作周波数を上げることができないということである。 機械学習スコアリングでは、2つの形式の並列性をし応して、この問題を解決しようとしている。 1つはアプリケーションの並列性を利用して、マシンの得られるパイプラインを使って処理をパイプライン化している。 ランキングでは、ステージ当たり8usが限界であった。 2番目の並列性は、殆ど見ることのないMultiple Instruction Streams, Single Data Steram(MISD)並列性である。 これは、非常に多くの独立した命令ストリームを動作させ、1つのドキュメントを処理するというものであった。

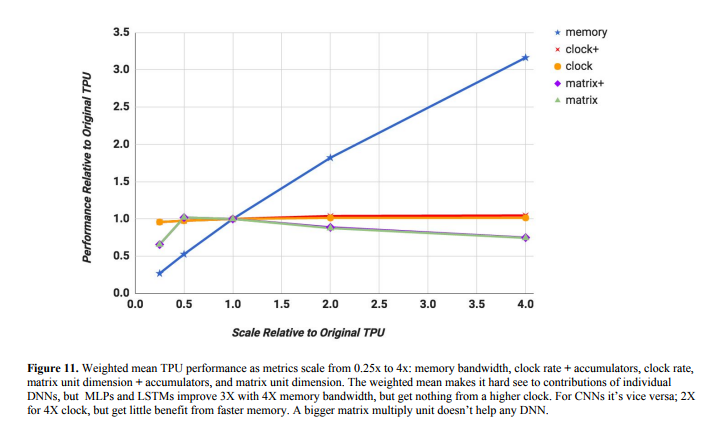

図7.24はCatapultのランキング関数の性能を示している。 7.9節でみるように、エンドユーザ向けのアプリケーションでは厳しいレスポンスタイムが要求される; 締め切り時間を過ぎると、いくらスループットの高いシステムでも出目なのである。 x軸はレスポンス時間の限界地であり、1.0以上となってはならない。 最大レイテンシで言うと、CatapultはホストのIntelサーバに対して1.95倍高速であった。