HPCA2024で開催された、RISC-Vのアウト・オブ・オーダCPU XiangShanについての資料が公開されていたので、読んでみることにした。 じっくり読みたいので、1ページずつ要点を抑えていく。

次は、マイクロアーキテクチャのトピックについて。続き。

- バックエンドの構成

- 命令フュージョン

- 隣接しているuOPsを結合する。

- RV64GCとRV64GC-Fusedで4%の命令削減、RV64GCBからRV64GCB-Fusedで2%の命令削減。

- Rename & Move Elimination

- 単純なmove命令は、リネームマップの差し替えにより実現する。

- Reservation Stationの構成

- 2-input & 2-output / 1-input & 1-outputの構成

- Age Matrixベースの命令選択

- FPUの構成

- IEEE 754互換の浮動小数点実行ハードウェア

- FPUはCascade FMAを実装。

- FADDのDelayは5サイクルから3サイクルに削減。

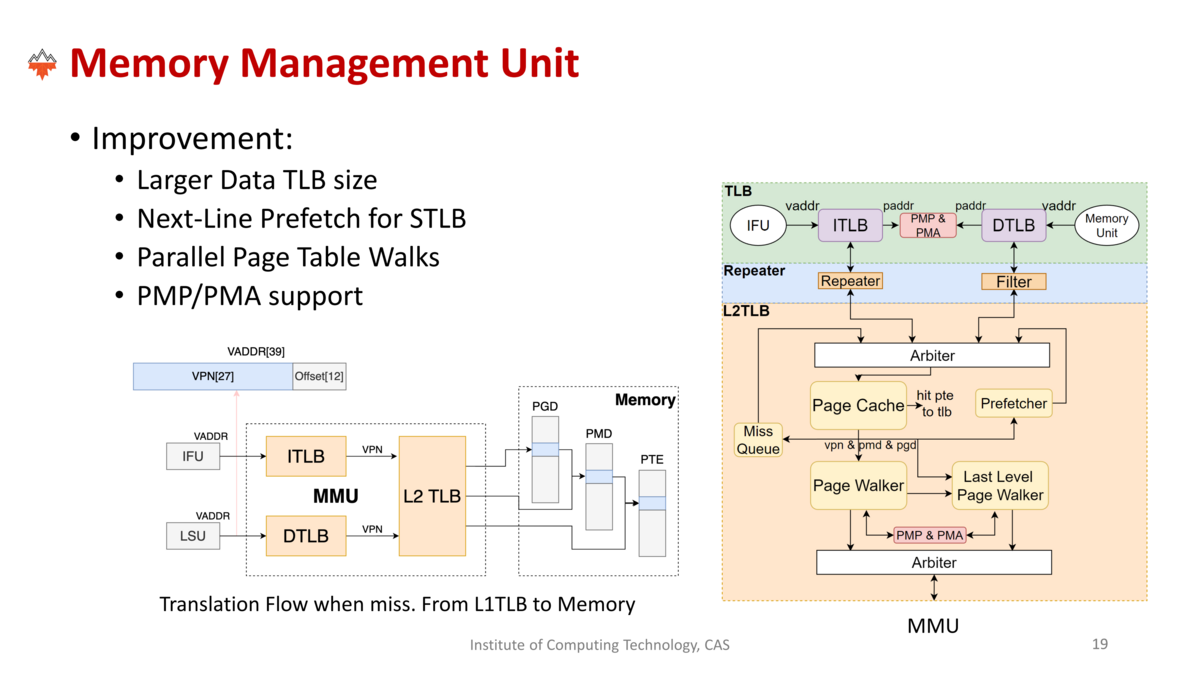

- MMUの構成

- STLB向けにNext Line Prefetcherを実装

- Page Table Walkを並列実行

- PMP / PMAをサポート

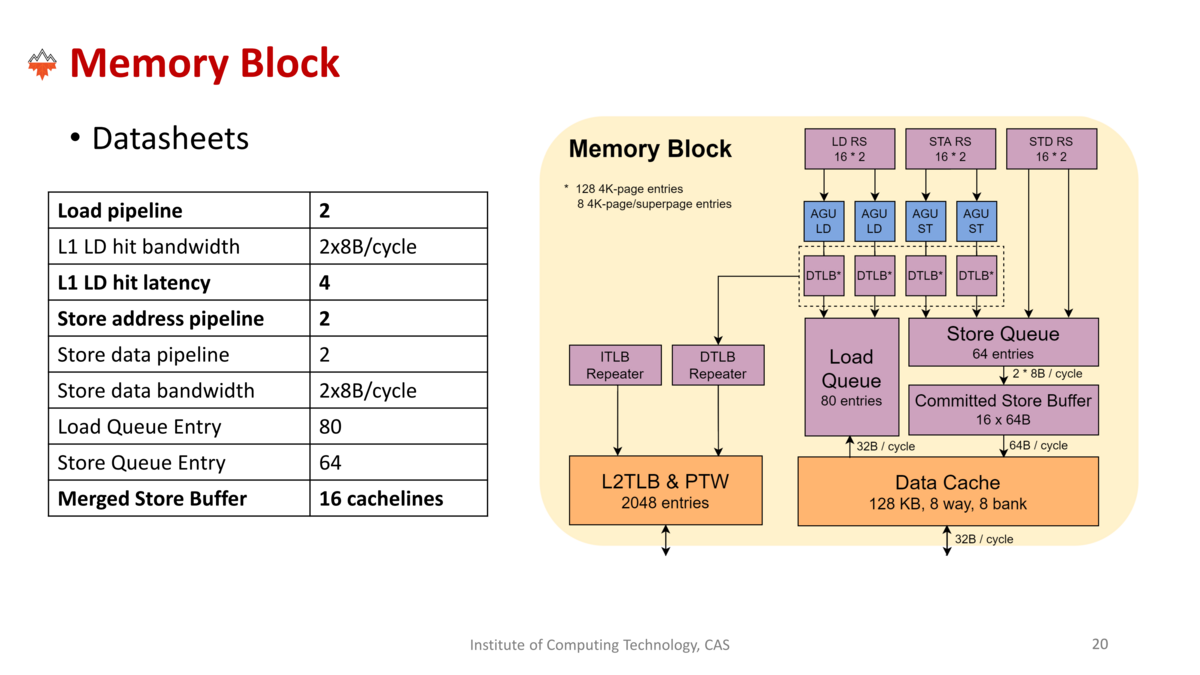

- メモリ・アクセスのブロック

- ロードパイプラインは2本用意

- LDヒットレイテンシ:4サイクル

- ストアアドレスパイプライン:2

- ストアデータパイプライン:2

- ストアデータのバンド幅 : 2x8B/cycle

- マージバッファ:16キャッシュライン

- ロード・パイプライン

- 4ステージ構成

- L1 Dキャッシュ

- ライトバック・キューはどういう仕組みだろう?

- L1 Dキャッシュ

- バンクを分割し、複数リードポートを持っている。