HPCA2024で開催された、RISC-Vのアウト・オブ・オーダCPU XiangShanについての資料が公開されていたので、読んでみることにした。 じっくり読みたいので、1ページずつ要点を抑えていく。

現在、オープンスタンダードとして知られるRISC-Vは、企業がどのようにチップを作るかという手法を変える可能性がある。

オープンソースソフトウェアエコシステムの成功を模倣し、ハードウェアもオープン化できないか?

チップ設計のバリアを低減するために、IPやEDAツールのコストを抑えることが肝要。

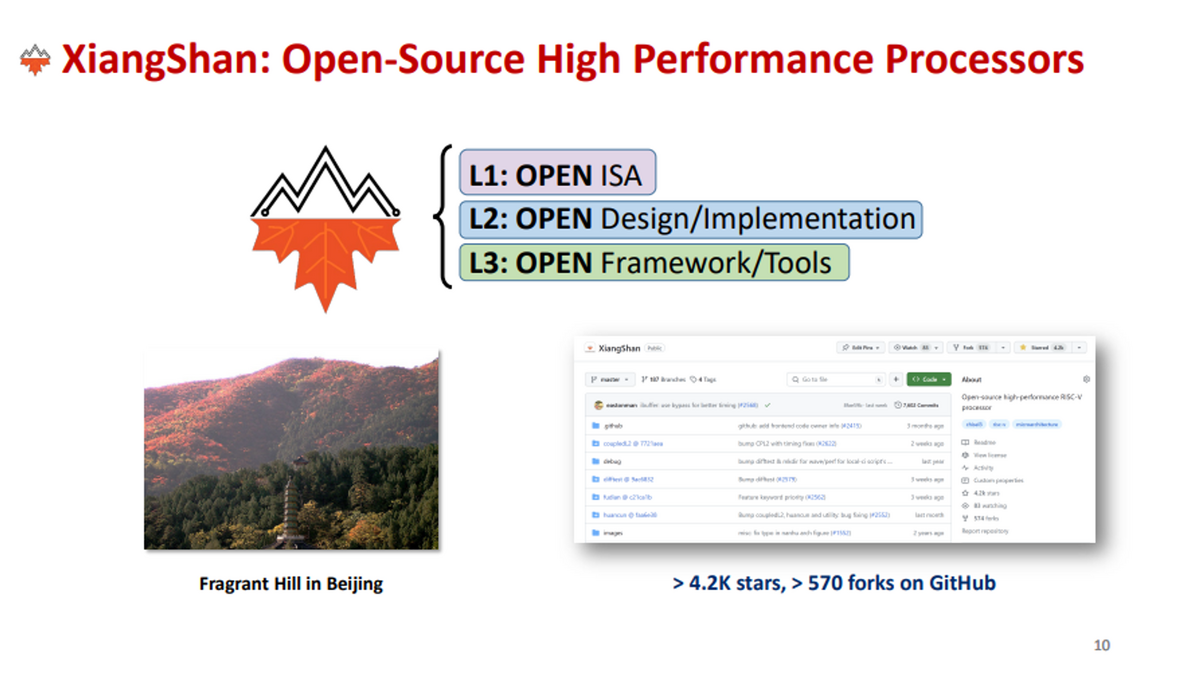

オープン・ソース・チップの3つの段階:

- ISAがオープン

- 設計、実装がオープン

- フレームワーク・ツール(この場合はEDAツールなど)がオープン

それぞれが、このように対応する。

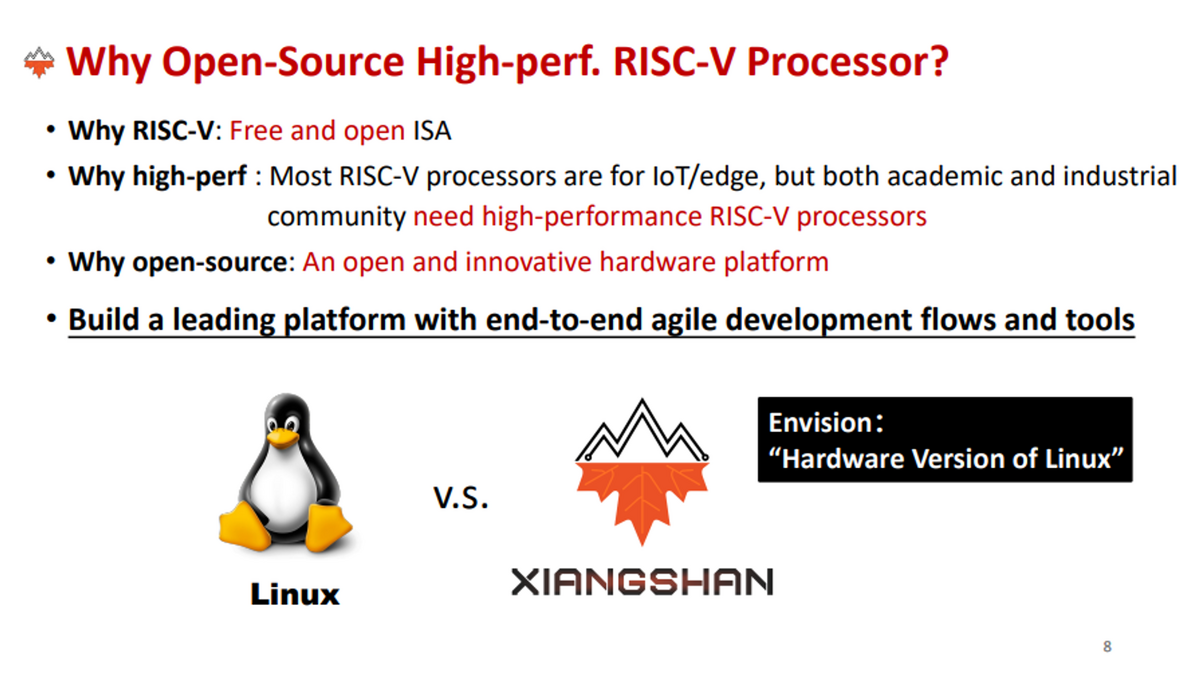

オープン・ソース・ハイパフォーマンスRISC-Vプロセッサがなぜ必要か?

- RISC-VはフリーでオープンなISA

- 多くのRISC-VコアはIoT/Edge向けだが、アカデミックや産業計は高性能RISC-Vプロセッサを望んでいる。

- オープンでイノベーティブなハードウェアプラットフォームを提供することによって、ハードウェア界隈を変えていくという目的がある。

- 「Linuxのハードウェア・バージョン」

XiangShanは北京にある香山に由来する。

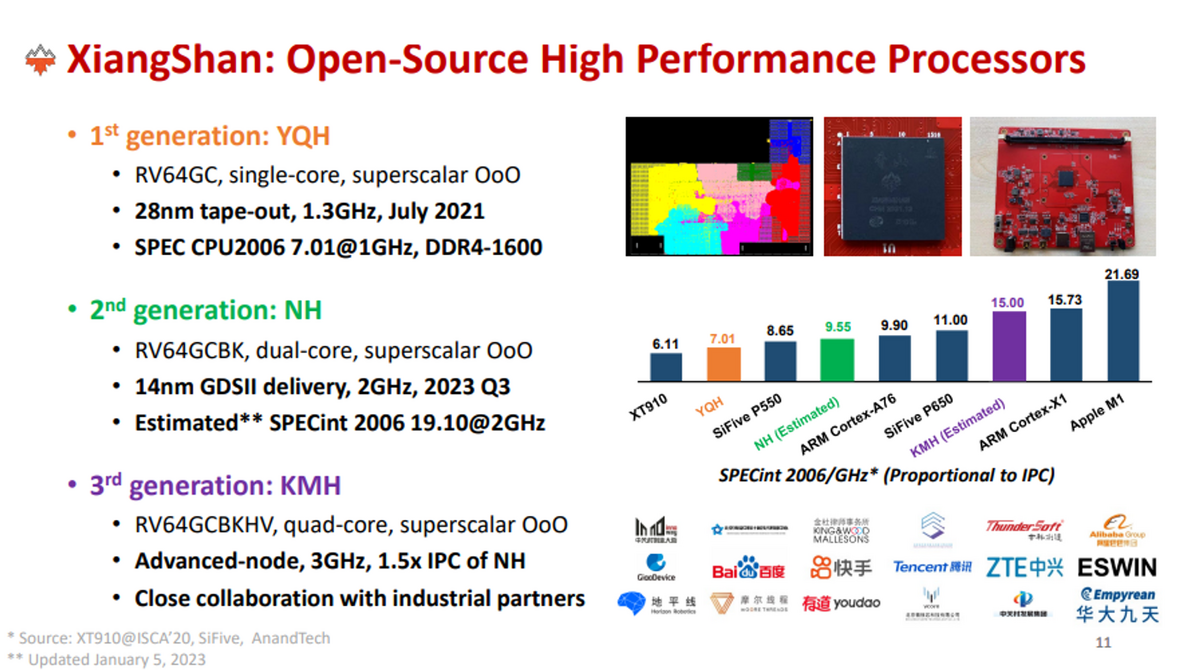

XiangShanは3つのバージョンが存在する。

- YQH

- RV64GC スーパスカラOoO シングルコア

- 28nm テープアウト済み

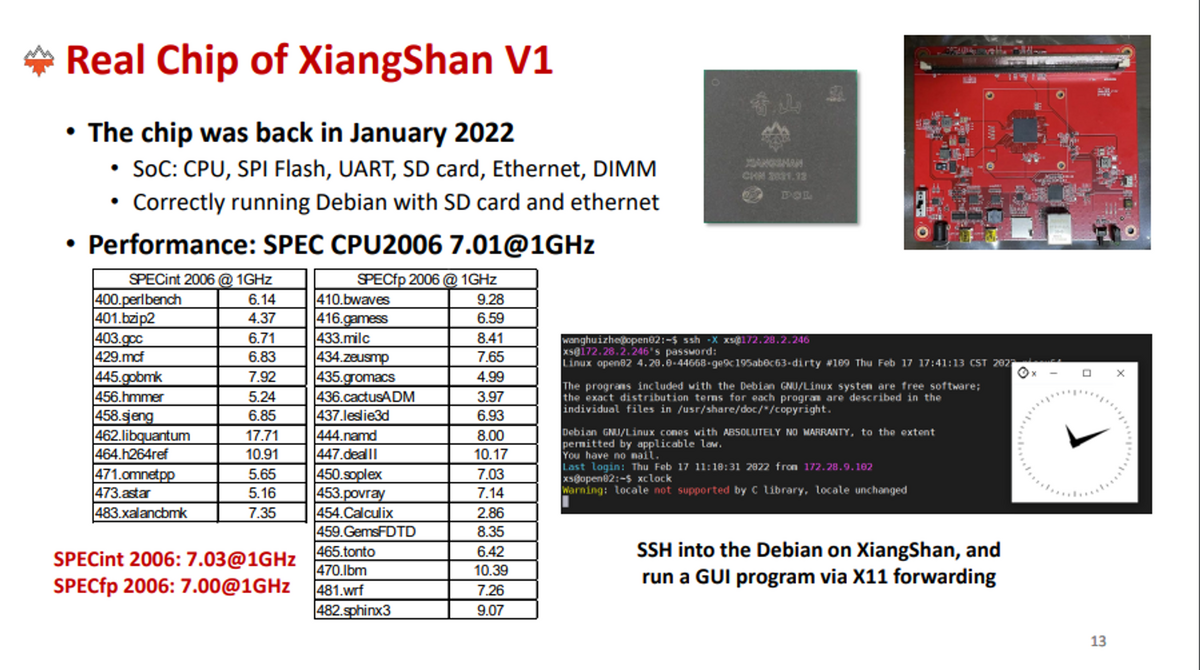

- SPEC CPU 2006 7.01@1GHz

- NH

- RV64GCBK スーパスカラ OoO デュアルコア

- 14nm テープアウト予定、2GHz動作

- SPECint 2006 19.01@2GHz

- KMH

- RV64GCBKHV スーパスカラ OoO クアッドコア

- 3GHz動作、NHの1.5倍のIPC

- インダストリアルと綿密な連携

第1世代のXiangShan (Yanqihu) はRV64GCの11ステージ・アウトオブオーダ・スーパスカラ

- 5.3Coremark / MHz

- SPEC CPU 2006 7@1GHz with DDR4-1600

XiangShan V1は2021年にテープアウトされ、2022に実チップ動作確認。

XiangShan V2 (Nanhu) は以下の変更を加えている。

- フロントエンドの向上:命令フェッチと分岐予測ユニットを分離。

- バックエンドの向上:スケジューラの向上、命令フュージョン、Move Eliminationなど

- L2/L3キャッシュ:ハイブリッド・プリフェッチャの導入

- デュアルコアへの構成変更:RV64GCBK

XiangShan V2は、SPECにおいて更なる性能向上を見込んでいる。FPGAでの検証をベースにした結果。

FPGAでのプロトタイプ実証の結果。

XiangShan V3 (Kunminghu) はARM Neoverse N2をターゲットとし、3GHzでSPECCPU 2006 45を目指す。

さらに、ハイパーバイザ・ベクトル命令のサポートを目指す。

XingaShan V3の変更点:

- 機能向上

- ハイパーバイザ・ベクトル命令のサポ―tお

- CHIプロトコルのサポート

- 性能向上

- フロントエンド・バックエンド・ロードストアユニットおよびキャッシュの性能向上

- RTLより計測されたパフォーマンスモデルの作成

- パフォーマンスモデルによる性能検証からの、RTLのファインチューニング

- 機能検証

- 階層検証フローおよびFPGAによるプロトタイプ

- 産業レベルの検証環境の導入

- 物理設計

- 物理設計チームの導入

- RTLコーディングの同じイタレーションで、タイミング評価を行う。

XiangShan V3は、SPECにおいて更なる性能向上を予測している。

XiangShan V3は、性能においてNeoverse V2の相当する性能を予定している。

XiangShanのBig CoreとMid Coreを用意することによって、デュアルコア構成環境を想定している。