勉強のためにOpenXiangShanのドキュメントを読む。原文は中国語なので、翻訳しながらまとめていく。

XiangShanのフロントエンドについて読んでいく。これ、前に少し読んだ分岐予測器と命令フェッチを分離するアーキテクチャかなあ?

フロントエンドの構成

分岐予測と命令キャッシュを分離するフェッチアーキテクチャとなっている。

分岐予測ユニット(Branch Prediction Unit)は命令フェッチ要求をキュー(FTQ: Fetch target queue)に書き込み、FTQはそれを命令フェッチユニットと命令キャッシュに送信する。

フェッチされた命令はプリデコードによって分岐予測エラーが無いかをチェックされる。その命令は命令バッファに送信され、デコードモジュールに渡されてバックエンドに送信される。

分岐予測

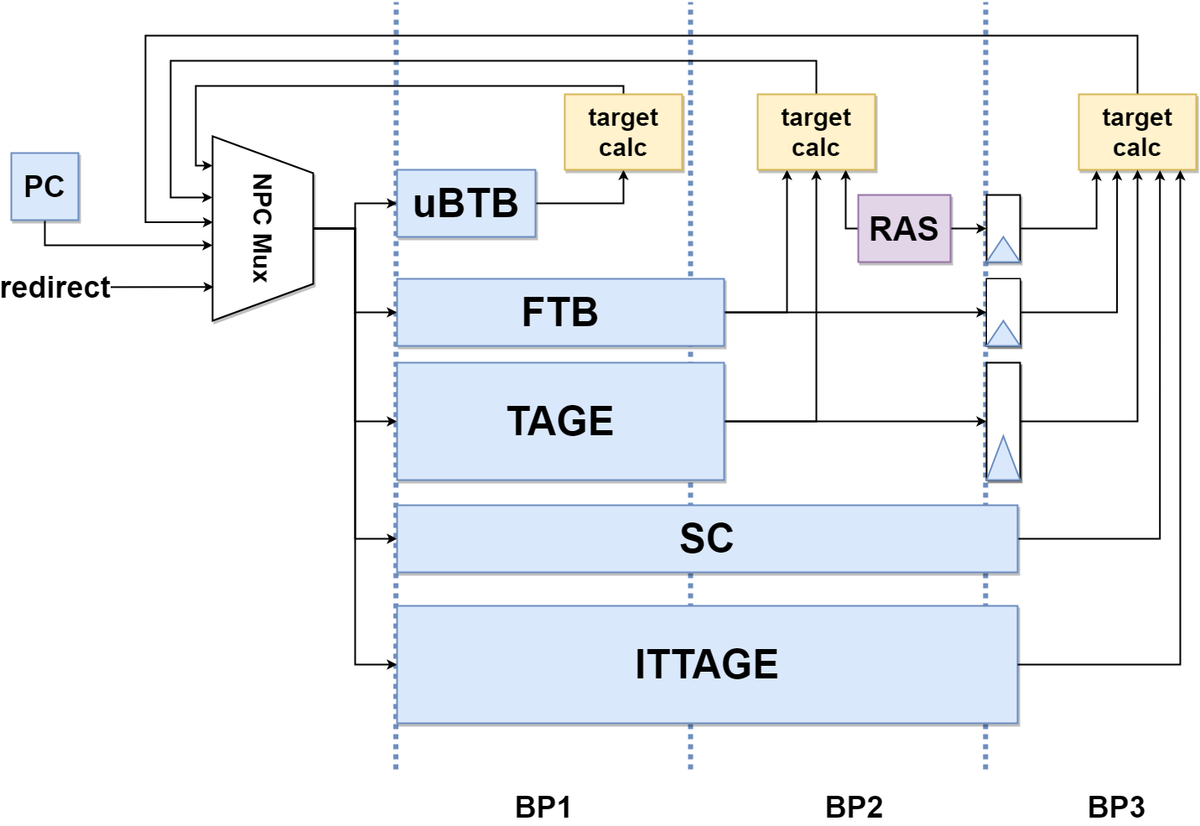

分岐予測ユニットはマルチレベルハイブリッド分岐予測アーキテクチャとなっている。

- Next Line Predictor (NLP)

- 0サイクルでの予測を可能とする分岐予測器。

- uBTB : マイクロBTB

- Accurate Predictor (APD)

- 2~3サイクルかけて分岐予測器

- FTB : 2サイクル

- TAGE-SC : TAGEは2サイクル, SCは3サイクル

- ITTAGE : 3サイクル

- RAS : 2サイクル

- 前世代(Yanqi Lake)と現世代(Nanhu)の違いは、分岐予測ブロックの定義方法である。

- BTBはFTBに置き換えられた。FTBアイテムは分岐予測ブロックを生成し、次のブロックの開始アドレスを予測するだけでなく、現在のブロックの終了点も予測する。

BPUトップモジュール

BPU内では各ステージはFTQに接続されており、各ステージの予測結果をFTQのハンドシェーク信号により設定する。

グローバル分岐履歴管理

グローバル分岐履歴管理とは、命令ストリーム中のすべての条件付き分岐命令の実行結果がシーケンシャルに管理されていること。

Next Line Predictor (NLP)

0サイクルでの予測は、uBTBによって実現される。PCに対して、予測ブロックの全体的な予測を行う。

分岐履歴とPCの下位XORインデックスを利用してテーブルに情報を格納し、テーブルから読み取られた情報nextAddrによって、分岐命令のジャンプが発生するか同課に関わらず次の予測ブロックの開始アドレスを含む予測を生成する。

- taken : ジャンプを行う

- takenOnBr : 条件分岐によるジャンプかどうか

- brNumOH:ブロック内の分岐命令の数を示す