モデルおよびBOOMv3に比べてどうも分岐予測の精度が悪い気がしているので、いろいろと調査していた。

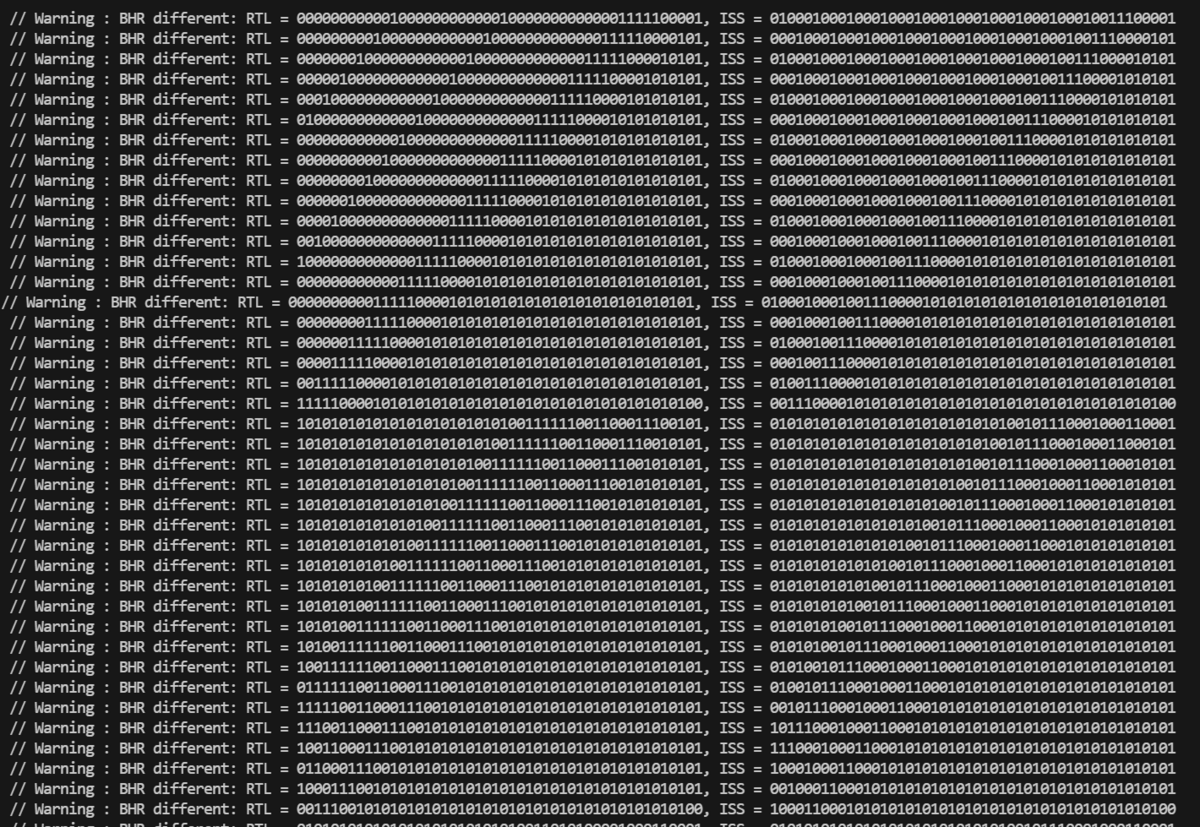

どうしてもモデルとの比較結果が異なるので、もうちょっと考え直さないとだめだ。 もっと詳細にログをとると、Gshareはグローバル履歴をかなり正確にとらないと正しい予測ができないということがわかってきた。 Gshareのグローバル履歴を汚してしまう理由としてはいろんなものがある:

- 投機フェッチによりGshareが汚れてしまう:

- これを防ぐためには、とりあえず投機的に更新されたgshareのグローバル履歴をバックアップしておき、投機実行が失敗する(その時点で命令がmispredictを通知する)と、グローバル履歴のビット列をロールバックして、さらに正しい情報に更新する必要がある。

- Non Conditional分岐による外乱:

- これは、RASによる予測が別のステージにより挿入されてしまうことが原因。Call/Retが検出されると、Call/Retがフェッチされたタイミングのグローバル履歴まで戻す必要がある。