モデルおよびBOOMv3に比べてどうも分岐予測の精度が悪い気がしているので、いろいろと調査していた。

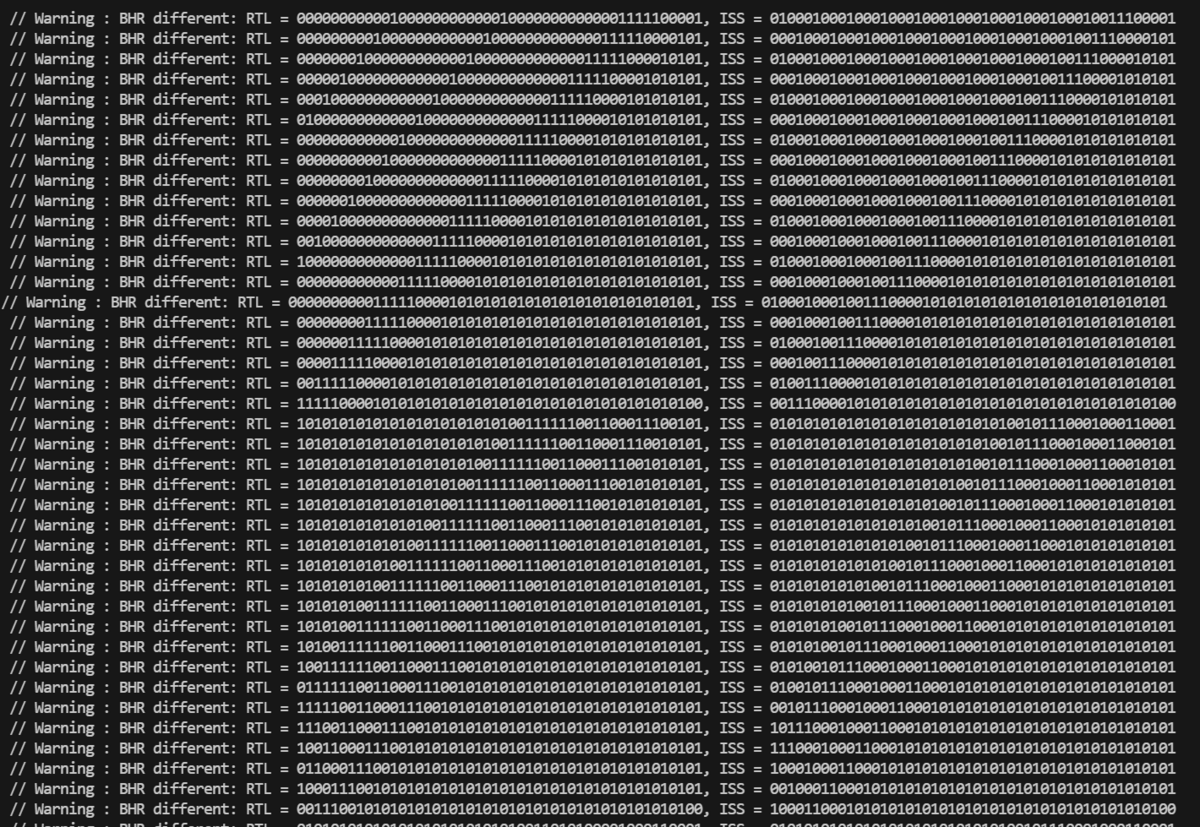

結果としては、グローバル履歴の更新に問題があり、正しく分岐予測のテーブルにアクセスできていないっぽい。 問題となるのは、以下のシンプルなループで、20回に1回分岐がNot Takenになるようなループ。1回のイタレーションの中に分岐命令が2つあるので、過去の40個の分岐の記録が取れれば、グローバル履歴から分岐予測が正しく生成できるはずだ。

000000008000353c <strcmp>:

8000353c: 00054783 lbu a5,0(a0)

80003540: 0585 addi a1,a1,1

80003542: 0505 addi a0,a0,1

80003544: fff5c703 lbu a4,-1(a1)

80003548: c799 beqz a5,80003556 <strcmp+0x1a>

8000354a: fee789e3 beq a5,a4,8000353c <strcmp>

8000354e: 0007851b sext.w a0,a5

80003552: 9d19 subw a0,a0,a4

80003554: 8082 ret

80003556: 4501 li a0,0

80003558: bfed j 80003552 <strcmp+0x16>

シミュレータでGshareの動作をシミュレーションしてみると、少なくともグローバル履歴を正しく更新できているのならば、すべての分岐を正しく予測できているはずだ。

問題は、投機実行のせいでグローバル履歴がずれてしまっているところだ。これをどうにかして修正しなければならない。でないと分岐予測の精度が大きく落ちてしまっている。