自作CPUに接続するサイクル精度シミュレータとしてSniperを使用しているが、Sniperは物理レジスタのサイズを考慮していない。つまり物理レジスタは無限に用意されている(あるいはROBのサイズに応じた適切な物理レジスタが用意されている)という仮定にある。 いろいろ物理レジスタの構成をいじってみたいので、ちゃんとした物理レジスタモデルを用意してSniperの再実行を行ってみた。

といっても、物理レジスタの実装はFreelistの代わりになるカウンタを用意して、freelist>0である限りディスパッチを許し、コミット時に回収するだけのinc/decカウンタをつけておけばよい。 Sniperに少しの変更を加えて、Dhrystone/Coremarkの性能を確認した。

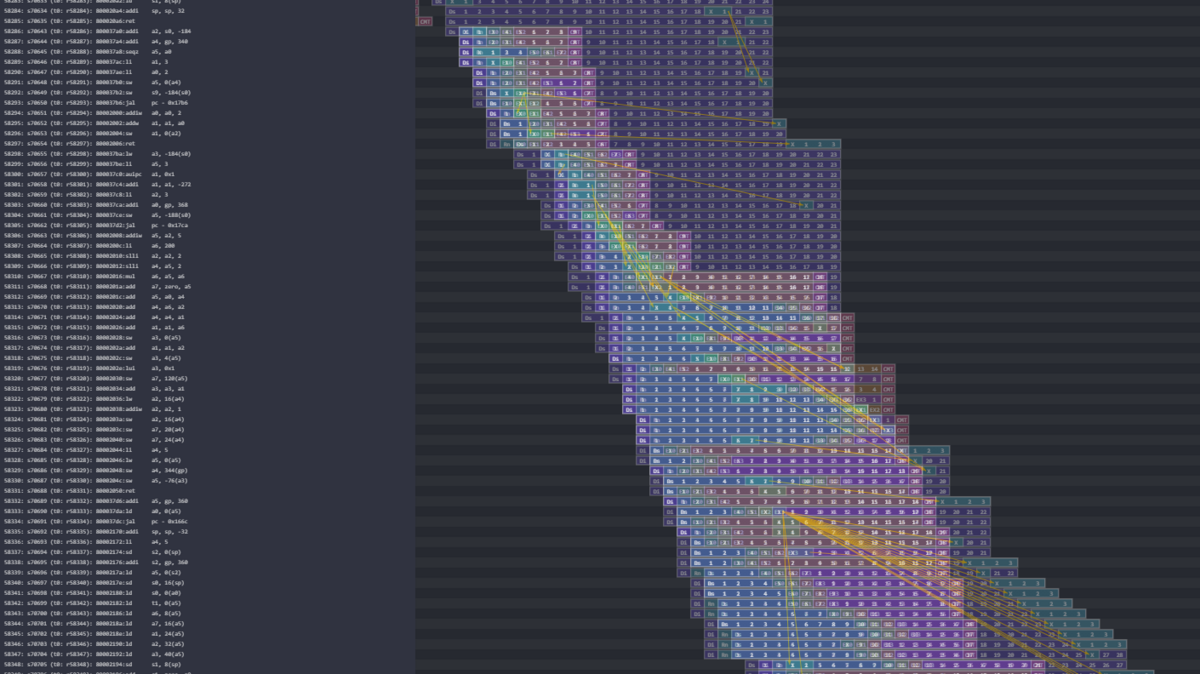

物理レジスタのサイズを48/64/128/256と変化させて性能を測定した。 Sniperは命令ウィンドウのサイズに応じてROBのサイズも変わるような設定になっており、ROBのサイズを物理レジスタを十分につ活用できる程度に大きさを変えながら、性能を変えていった(なお、ROBのサイズを固定して物理レジスタのサイズを変えても傾向は同じであった:少し性能の伸びは小さくなった)。

結果は以下の感じで、Coremarkで物理レジスタのサイズを制御することによって20%程度性能のぶれが発生することが分かった。 ここで確認したかったのは、物理レジスタの大きさや割り当てのタイミングで性能が変わることが確認したかったので、これで良しとする。