「A Pluggable Vector Unit for RISC-V Vector Extension」という論文を読んでみたのでそのメモ。 本当はRISC-Vベクトル実装の一例として内容を知っておきたかったのだが、あんまり詳細に説明がないうえに、いろいろと問題になるところを説明していないぞ?

とりあえず前半を読んでみることにする。

https://ieeexplore.ieee.org/document/9774501

https://dl.acm.org/doi/abs/10.5555/3539845.3540113

本論文では、RISC-Vベクトル拡張RVV1.0を実装したコアのマイクロアーキテクチャを紹介するものである。CVA6をベースとし、ベクトル命令の投機的な実行と正確な例外をサポートしている。

実装の詳細について概説し、合成結果について定性的・定量的な考察を行う。

本研究では、V拡張の再利用可能で効率的な実装を紹介する。提案する設計は、スカラーコアの機能ユニットとして統合されることを意図している。我々のターゲットコアはCVA6 [6]である。

本研究では、ベクトル拡張の再利用可能で効率的な実装を紹介する。スカラコアの機能ユニットとして統合されることを意図しており、ターゲットコアとしてCVA6を使用する。 しかし、CVA6を使用することは我々の提案とは無関係である。本論文で紹介するマイクロアーキテクチャでは、ベクトル命令のアウトオブオーダ実行と、正確なベクトル例外をサポートしている。サードパーティ製演算ユニットを低集積オーバヘッドでホストできることを示す。

- アーキテクチャの詳細について

スカラコアの実行ステージで、機能ユニットとして簡単に結合できるベクトルユニットの設計を考える。スカラコアとの依存関係は、可能な限り最小化する。

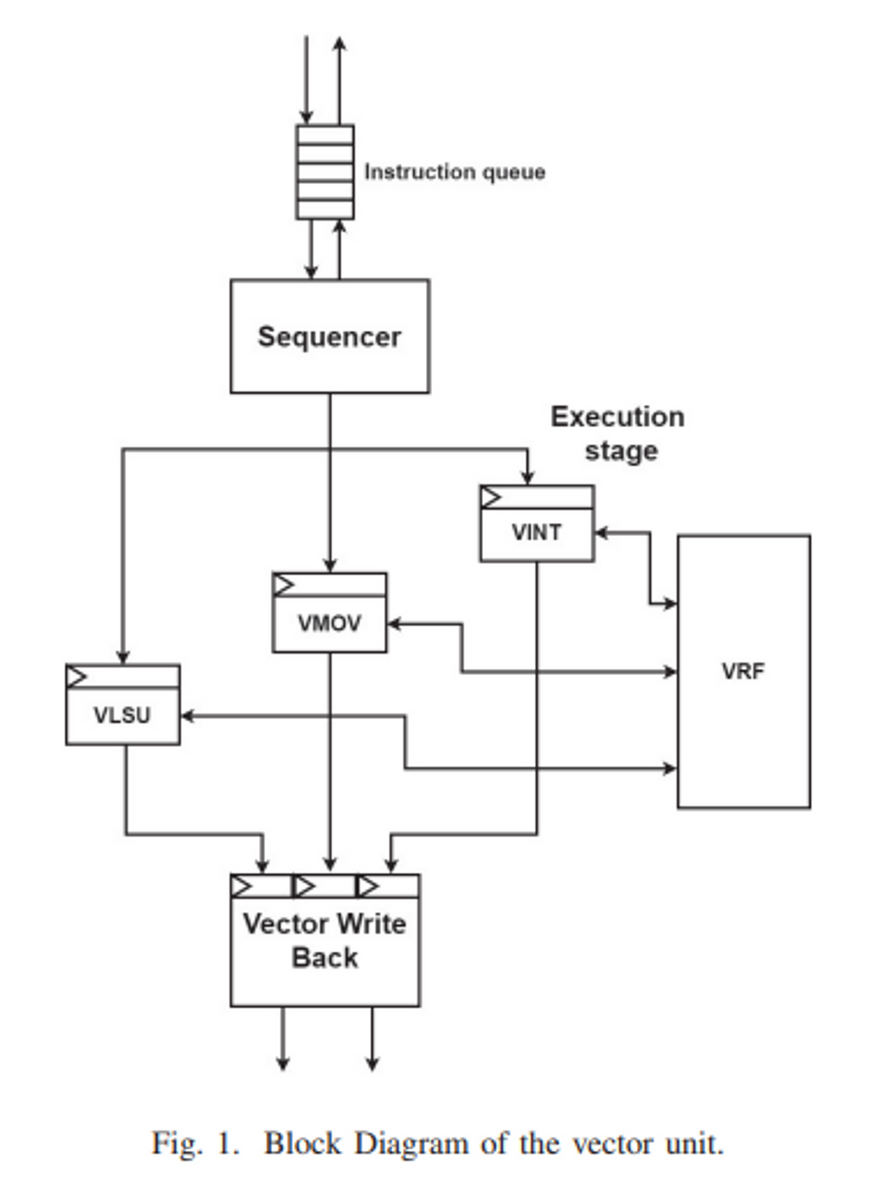

ベクトルユニットは3つのステージに分解されている。シーケンサ・実行ステージ・ベクトルライトバック

シーケンサは命令を受け取り、ベクトルレジスタファイルの読み込みを行って実行ステージに命令を転送する。

ベクトル命令の投機的実行と正確なトラップをサポートしている。ベクトル命令の内部アーキテクチャは、マイクロプログラムされたSIMDパイプラインを利用する。

- スカラRISC-Vコアとの接続について

CVA6をスカラコアとして扱い、ベクトルユニットを結合する。CSRパイプラインによってベクトルCSR更新命令が実行され、その間ベクトル命令はストールする。