Flexible Timing Simulation of RISC-V Processors with Sniperという論文を読んでいる。SniperのRISC-V対応に関する初期の論文だ。2018年の論文なので実装はもう少し進んでいるはず。

Sniperについて、インターバル・シミュレーションをベースとした次世代の並列マルチコア・オープンソース・シミュレータである。

最初はIntel x86 ISAをサポートしていたが、追加のアーキテクチャを柔軟にサポートするためのSniper基盤の拡張を説明する。Sniperに新しいISAを追加することで、柔軟に解析や拡張を行うことができるようになる。

- ISA機能シミュレータ

- Spike

- 古システム・エミュレータ

- タイミング・シミュレータ

- FireSim / Gem5

- rv8シミュレータ

Sniperは並列マルチコアシミュレータである。

通常は、SniperはIntelのPinのツールとして実行され、ターゲットマイクロアーキテクチャのタイミング結果を生成する。

スタンドアロン再生モードでは、Sniperを使用して命令トレースを収集し、再生することができる。

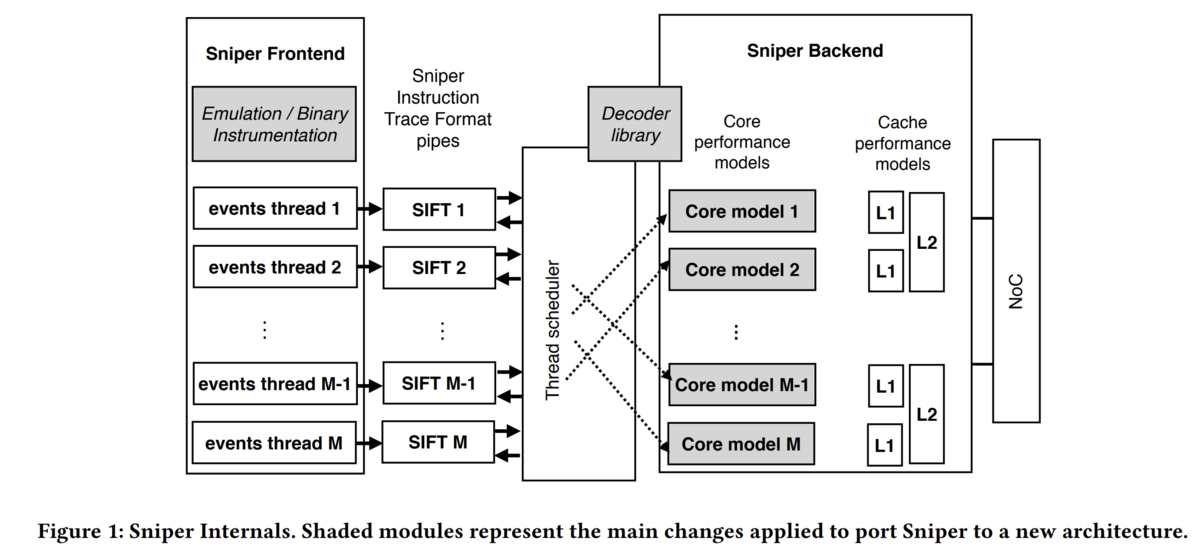

Sniper Instruction Format Tool(SIFT)は、収集されてディスクに保存されるか、オンザフライで生成され、フロントエンドとバックエンドのSniperコンポーネント間の双方向通信に使用される。

この方式によれば、1つのタイミング・シミュレータで複数のワークロードを実行するために使用することができる。SIFTベースの接続により、様々なツールをSniperのフロントエンドに使用できるようになる。この結果、RISC-VアーキテクチャをSniperに移植することが検討されている。

Sniperの大局的な構成:

- フロントエンド

- どうやらトレースファイルからイベントをとらえてSIFTなどのフォーマットに置き換えるらしい?

- Control : 通信ファイル(SIFT)をオープン/クローズし、インスツルメンテーション・モードを早送り、ウォームアップ、詳細シミュレーションの間で変更するモジュール。例えば、アプリケーションの関心領域(ROI)のみを詳細にシミュレーションする場合、ROIの外側のコードセクションは、機能的なキャッシュウォーミングモード(ROI実行前にメモリサブシステムをウォームアップする)でシミュレーションするか、キャッシュウォーミングモードなしで早送りをすることができます。

- Instruction Instrumentation Callback: 実行された各命令をインターセプトするモジュール。早送りモードでの命令カウント、詳細インスツルメンテーションモードでのSIFTフォーマットに必要な命令情報の送信、マジックインストラクション(プロセッサのアーキテクチャの状態を変更しないが、アプリケーションコードがSniperバックエンドと通信するために使用する特殊な命令。)

- System call’s instrumentation: システムコールを傍受し、Sniper backendにシミュレーションさせるためのモジュール。

- Thread instrumentation: スレッドの生成、同期、終了を傍受するモジュール。

- SIFTトレース

- Sniperで使用するために開発されたトレースファイル形式。命令の実行順序が記述されているが、詳細なタイミングシミュレーションに必要なメモリアドレスなどの動的情報なども含まれている。

- バックエンド

- プログラムの実行を制御する。コアモデルはスレッドの進捗を推定し、キャッシュ改装と分岐予測器は実行駆動型性能モデルでモデル化される。

Sniperの抽象化モデルについて:

- コアの抽象化:インターバル・シミュレーションに基づくコアモデルを提供している。追加制約をモデル化できる命令ウィンドウ(IW)中心モデルをサポートしている。

- 完全なメモリ依存性の予測:シングルパスで実行するシミュレータでは実行不可能な完全なメモリ依存性の予測をサポートすることができる。

- オペレーティングシステムのエミュレーション:Sniperでの抽象的なシステム・モデリングが可能となる。

rv8とSpikeがSIFT生成をサポートするように更新された。

SIFTに対する大きなデータ構造の変更は必要なかった。

いくつか修正が必要なコンポーネント: