SystemVerilogのStreaming演算について、あまり良く知らなかったのでいろいろ勉強しようと思った。

Streaming演算では、任意のサイズでのビット列の反転ができるらしい。以下のサイトが参考になる。

https://www.amiq.com/consulting/2017/05/29/how-to-pack-data-using-systemverilog-streaming-operators/

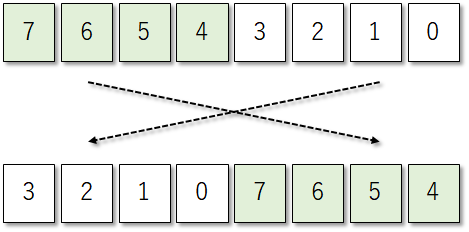

基本は1ビットずつ反転する場合。<<で使用できる。

module streaming; initial begin static bit [7:0] value_a = 8'h8C; static bit [7:0] value_b = {<<{value_a}}; $display("value_b = 0x%h", value_b); end endmodule // streaming

以下は4ビットずつ反転する例。

initial begin static bit [7:0] value_a = 8'h8C; static bit [7:0] value_b = {<<4{value_a}}; $display("value_b = 0x%h", value_b); end

これはpacked arrayに対しても適用できる。以下はpacked arrayのビットを全部反転させてしまう例。

initial begin static bit [7:0] array[2] = '{ 8'h8C, 8'hA4 }; static shortint value = {<<{array}}; $display("value = 0x%h", value); end

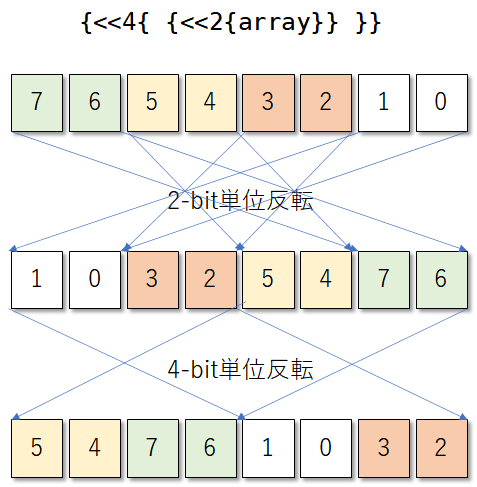

さらに変態的なのは、最初に2ビット単位で反転して、さらに4ビットずつ反転することができる。これはネットワークパケットの処理などで便利なのかもしれないが、普通のデータプロセッシングにおいてどのように役に立つのかはちょっと想像がつかない。

typedef struct { bit [3:0] addr; bit [3:0] data; } packet_t; initial begin static bit [1:0] array[] = '{ 2'b10, 2'b01, 2'b11, 2'b00 }; static packet_t packet = {<<4{ {<<2{array}} }}; $display("packet addr = %b", packet.addr); $display("packet data = %b", packet.data); end