CARRVというのはComputer Architecture Research with RISC-Vのことで、RISC-Vネタにした研究に関するワークショップである。 毎年ISCAと併設して実施されている。

なんかまじめに論文を読んでいなかったので、とりあえず概観してみることにした。

RISKA : SKAデータ処理向けのRISC-Vをベースとしたオープンソースのドメイン特化System-on-Chipに向けて

SKAとはSquare Kilometer Arrayの意味。RISKAというのはオープンソースのメニーコアSoCで、CPUコアとしてRISC-Vを採用している。このプロジェクトの目的は電波望遠鏡で取得した画像を解析するためのシステムを構築することである。SKAはRISC-V CPUコアとカスタムデザインアクセラレータから構成されている。

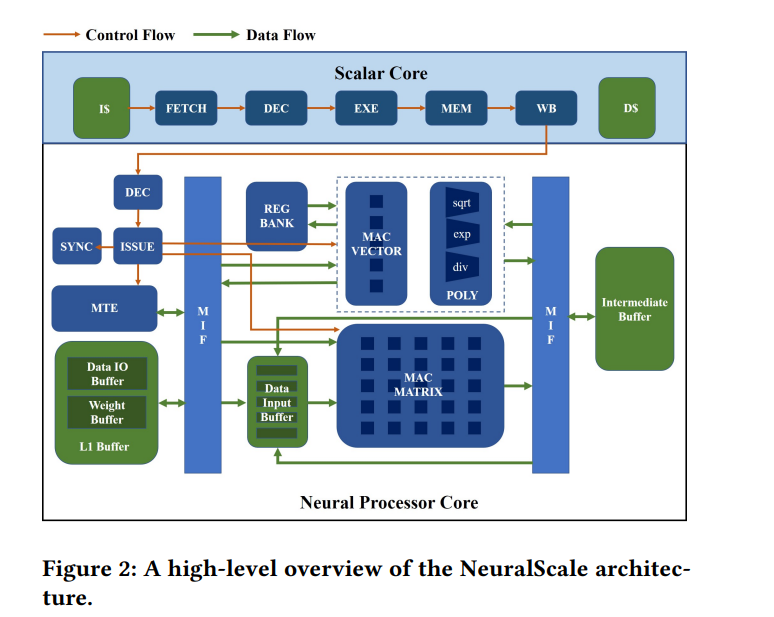

NeuralScale: クラウド上でAIの推論をブーストするためのRISC-Vベースのニューラルプロセッサ

NeuralScaleというAI推論向けのチップを開発した。

RISC-V データフローアーキテクチャ

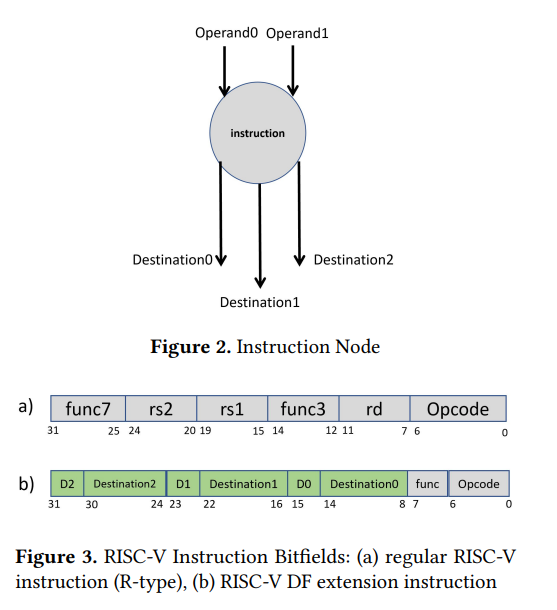

データフローアーキテクチャはフォンノイマンアーキテクチャとは別のもので、大きく分けて2種類のものがある。 - 明示的なデータフローアーキテクチャ: データフロー的な処理に対して高い性能を示す。 - ハイブリッドアーキテクチャ: フォンノイマンとデータフローのハイブリッド型

本研究で開発したのは、明示的なデータフローアーキテクチャに対してRISC-Vの移植を行ったものである。Gem5に対してこれを実装し、最大で7.5%の性能向上を達成した。

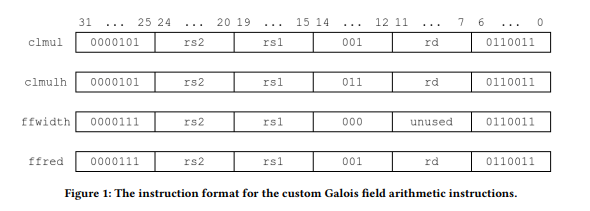

暗号および誤り訂正符号のための汎用RISC-V ISAガロアフィールド演算拡張機能

暗号処理のためにはガロア体演算をベースとしたアルゴリズムが求めらている。ガロア体演算乗算用RISC-V命令セットを実装して動作させた。 AESやReed-Solomonコードのようないくつかのアルゴリズムでは性能の向上が確認できた。