この記事は 半導体・ハードウェア開発 Advent Calendar 2017 - Qiita の2日目の記事です。

Advent-Calendarを埋めてくれるかた、今からでも募集中です!是非参加してください! 私一人では、クオリティのある記事を続けられそうにありません。。。(弱音)

2017年は、特にRISC-Vにとって重要な年になった。

商用IPを販売するSiFive社が本格的なSoCを投入し、RISC-V Foundationの加盟グループも100を超えてきた。 RISC-V FoundationのPlatinum Membersにも、巨大企業が名を連ねており威厳が増してきている。

RISC-V Foundationの加入メンバーは2017 Q3で100を突破した。

RISC-V Ecosystem Surpasses 100 Members Globally, Paving the Way for the Next 50 Years of Computing Design and Innovation - RISC-V Foundation via kwout

また、多くの半導体ベンダがRISC-Vに対応したハードウェアIP、ソフトウェアツールなどをリリースし始めている。

プロセッサをたしなむ人たちにとってのバイブル、「ヘネパタ」こと「コンピュータアーキテクチャ・定量的アプローチ」の第6版も年内に出版される予定であり、こちらもRISC-Vに題材を移行して全体的に刷新される予定である。 少しずつではあるがRISC-Vは軌道に乗り始めた。

- 作者: John L. Hennessy,David A. Patterson

- 出版社/メーカー: Morgan Kaufmann

- 発売日: 2017/12/07

- メディア: ペーパーバック

- この商品を含むブログを見る

研究向けのチップ開発から、ソフトウェアエコシステムの構築、プロダクションへの浸透が進む

初期のRISC-V Workshopの頃に比べて、研究向けの発表というよりもプロダクトの発表が多くなってきた。 Crusoeを開発したDavid Ditzel氏が立ち上げたEsperantoが開発している、4KコアのRISC-Vプロセッサが大きくニュースに取り上げられている。

一方で、より学術研究向けのイベントとしてCARRV(Computer Architecture Research with RISC-V)が立ち上げられた。 こちらはプロダクト関連ではなく、IEEE MICROと連携した研究者向けのイベントとなる。 論文も公開されており非常にありがたい。

- CARRV (Computer Architecture Research with RISC-V )

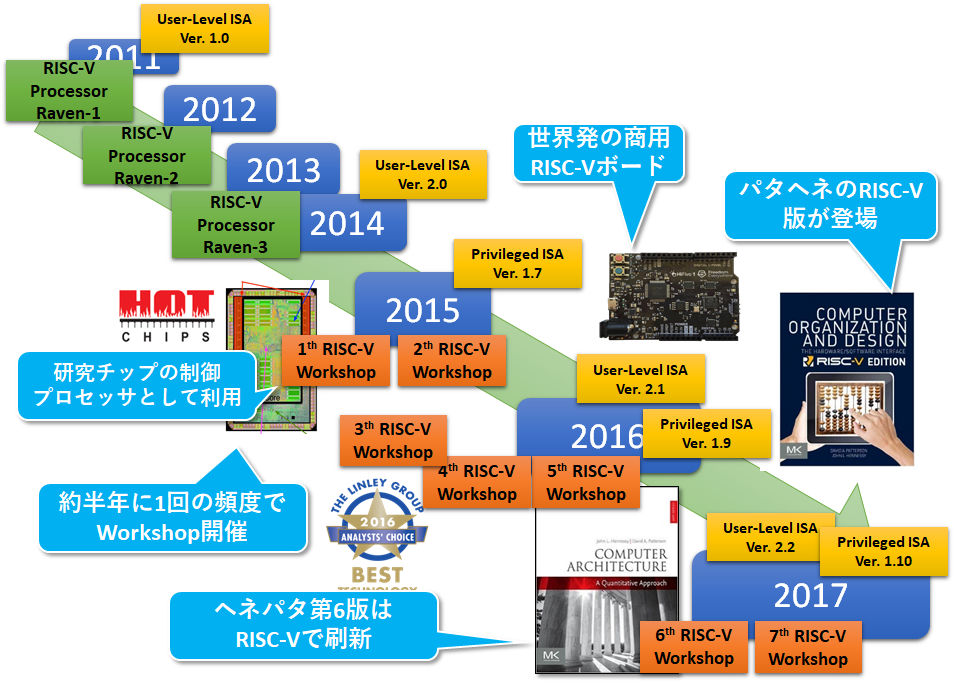

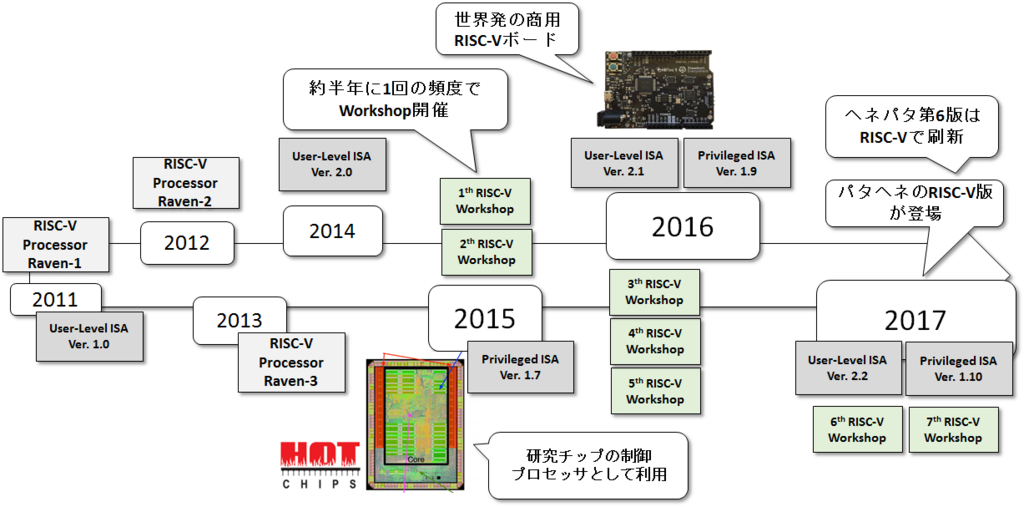

2011年から2016年のRISC-Vの発展の歴史

下記の画像は私が作った、2011年から2016年、2017年にかけてのRISC-Vの発展を示した資料だ。 最初は研究用として作られたRISC-Vも、仕様が公開されてその性能と使いやすさが認められてから、徐々に発展していることが分かる。

非常に強力なバックアップ

RISC-Vが発展するにあたり非常に重要なキーパーソンとなっているのが、MIPS、というかCPUの発展において非常に重要な役割を果たしている David Patterson氏のバックアップがあることだ。

David Patterson氏自身がRISC-Vを推しているということ、そしてRISC-V FoundationのChirmainであるKrste Asanović氏がPatterson氏の教え子であると言うところが大きい。

これにより、学術界にもRISC-Vは非常に大きな影響を与える。 「パタヘネ」と呼ばれるコンピュータアーキテクチャの入門書 "Computer Organization and Design" は RISC-V Editionが登場し、「パタヘネ」と呼ばれるより高度な内容を取り扱った書籍 "Computer Architecuter: A Quantitative Approach" は 12月に第6版が出版される予定で、これまでにMIPSで説明されていた内容がRISC-Vに全面的にアップデートされる予定となっている。

2017年に発表されたRISC-V実装

普段こういう情報をきちんとまとめていないので抜けがあるかもしないがご愛嬌。 プロダクトとして発表されたものを中心にまとめている。 学術研究としては非常に多くの実装がなされているが、数が多すぎるので省略。CARRVのウェブサイトを参照されたい。

SiFive U64-MC-Coreplex

RISC-Vと言えばSiFive。SiFiveのリリースした64ビットのマルチコアプロセッサがU54-MC-Coreplex IPだ。 RV64GC をサポートしたRISC-Vコアを4つ搭載しており、L1-ICache, L1-Dcacheをそれぞれ最大で32KB持つことが出来る。 また、モニタコアとして載っているRV64IMACをサポートしたシングルコアのRISC-Vプロセッサもあり、かなり本格的な利用を想定している。 また、Linuxもインポートさせ、動作させることが可能だ。

Andes Technology N25, NX25

Andes Technologyが発表したRISC-Vプロセッサ。 N25が32ビットコア、NX25が64ビットコアである。

N25のサポートする命令セットはRV32IMAC, NX25はRV64IMACとなっている。 どちらも基本的な⑤ステージパイプラインで、I-Cache、D-Cacheの構成は8KBから64KBまで変更が可能。 ILM, DLMを持っている。 5ステージのパイプラインだが、分岐予測機構を備えており、BTB(Branch Target Buffer), BHT(Branch History Table), RAS(Return Address Stack)を持っている。

性能的には - N25 2.86 DMIPS/MHz 3.46 CoreMark/MHz - NX25 3.20 DMIPS/MHz 3.45 CoreMark/MHz

Microsemi MI-V

https://www.microsemi.com/products/fpga-soc/mi-v-ecosystemwww.microsemi.com RV32IM RISC-Vを、MicrosemiのFPGAである PolarFire, RTG4, IGLOO2 で動かすことが出来る。

Esperanto Technologies ET-Maxion, ET-Minion

あまり細かい情報は載っていないが、ET-MaxionはRV64GC, ET-Minion はRV64G。 2018/01/26 ET-MinionをRV32と記載していました。ご指摘ありがとうございます。訂正しました。

Codasip Bk5-64

Codasip初の64ビットRISC-Vプロセッサは、命令セットとしてRV64I。ただしそれ以外の領域はかなり非サポート。 64ビットコアを作りたかったと言うだけで、それ以外は何も載っていない。

2017/12/18 "RISC-V Day Tokyo" 開催

日本で最初のRISC-V専門のイベントとして、"RISC-V Day Tokyo"が開催される。 - 2017年12月18日 9:30 - 18:30 - 東京大学 伊藤国際謝恩ホール

以下 https://riscv.tokyoから抜粋。

今回のカンファレンスは - ①IoT、AIシステム用ソリューションをFPGAとSoC+ソフトで高い自由度で経済的に商品化したい人 - ②既存マイコンシステムに飽きたら図応用アルゴリズムをハードでアクセラレーションをしたい人 - ③日本だけでなくグローバルに展開できるマイコンシステムを設計したい人 - ④32ビットに加え、64,128ビット数値処理、アドレッシング機能を使用したい人 - ⑤基板ソフト、開発ハード、量産ハード、開発ツールを経済的に調達したい人

に役に立ちます。とのこと。

riscv.org にもアナウンスが出てますね!

私も発表します。

@msyksphinz (FPGA日記著者) : "RISC-Vオープンソース ハードウェア 概説"